原标题:西部数据新发两款自主RISC-V核心:免费开放

说起西部数据,大家第一个想到的肯定是硬盘,但其实在CPU处理器领域,西数也是钻研颇深,2018年底就发布了基于RISC-V指令集的自主通用架构SweRV、开源的SweRV指令集模拟器(ISS),并向第三方芯片厂商开放。

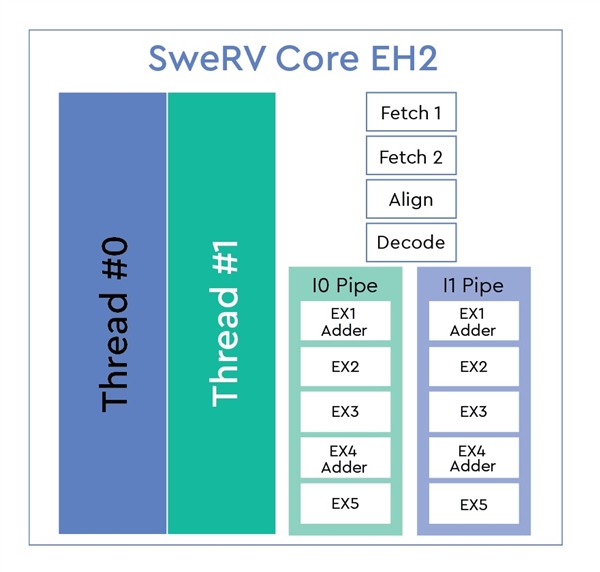

西数SweRV是一种32位顺序执行架构,双路超标量设计,9级流水线,支持SMT同步多线程。

第一个版本Swe Core EH1采用台积电28nm工艺制造,运行频率高达1.8GHz,模拟性能可达4.9 CoreMark/MHz,略高于ARM A15。

今天,西数发布了两款新的SweRV核心产品SweRV Core EH2、SweRV Core EL2,都属于微控制器专用CPU。

SweRV Core EH2基本架构不变,工艺升级为台积电16nm FinFET造,以获得性能、功耗、面积的最佳平衡,模拟性能提升29%达到6.3 CoreMark/MHz,内核面积缩小39%仅为0.067平方毫米。

它依然可用于SSD控制器等领域,而更强的性能、更小的面积使其应用潜力更大。

SweRV Core EL2是一个超级精简版,还是32位顺序架构、16nm工艺,但改成单路超标量、4级流水线、单线程,内核面积只有区区0.023平方毫米,性能约3.6 CoreMarks/MHz。

它主要用于取代控制器SoC中的时序逻辑、状态机,它们都必须尽可能的小。

西数表示,EH1、EH2、EL2核心都会在近期出现在大量产品中,但没有透露具体名单(或许自家SSD主控?),而这些核心都会继续对外开放,以壮大RISC-V的生态。

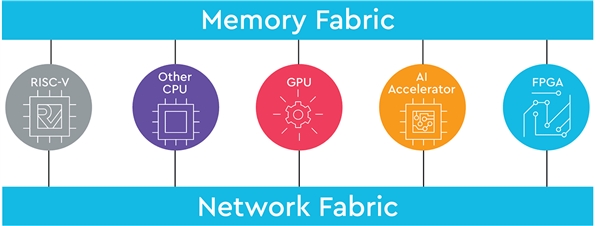

此外,西数还发布了基于以太网OminXtend的缓存一致性技术的硬件参考设计,开发者可引入自己的芯片设计中,比如GPU、FPGA、机器学习加速器等等。

西数已将此设计交给芯片联盟(Chips Alliance),后者今后将负责OmniXtend协议的进一步开发。

“掌”握科技鲜闻 (微信搜索techsina或扫描左侧二维码关注)