来源:内容由半导体行业观察(icbank)编译自「anandtech」,谢谢。

日前,Western Digital已为其SweRV微控制器CPU 产品组合中增加了两个新的处理器内核SweRV Core EH2和SweRV Core EL2 。并且,与过去的保持一致,该公司已免费向行业提供了其RTL设计。此外,该公司还推出了第一个基于以太网协议的OmniXtend缓存一致性存储器的硬件参考设计,并将该架构的管理和支持转移给了Chips Alliance。

SweRV内核EH2是设计用于微控制器的32位有序内核。它使用带有9级流水线的2路超标量设计和2路同时多线程功能。从本质上讲,EH2是去年推出的EH1的性能增强版本,支持SMT,使用TSMC的16 nm FinFET制造技术制造,以实现最大的PPA(功率,性能,面积)效率。EH2内核应提供6.3 CoreMark / MHz(基于Western Digital的仿真结果),高于EH1的4.9 CoreMark / MHz,使用上述工艺生产时,其尺寸仅为0.067mm²(相比之下,EH1在28 nm仅做到0.11mm²)。)。SweRV Core EH2将用于与其前身相同的应用程序(例如SSD控制器)。

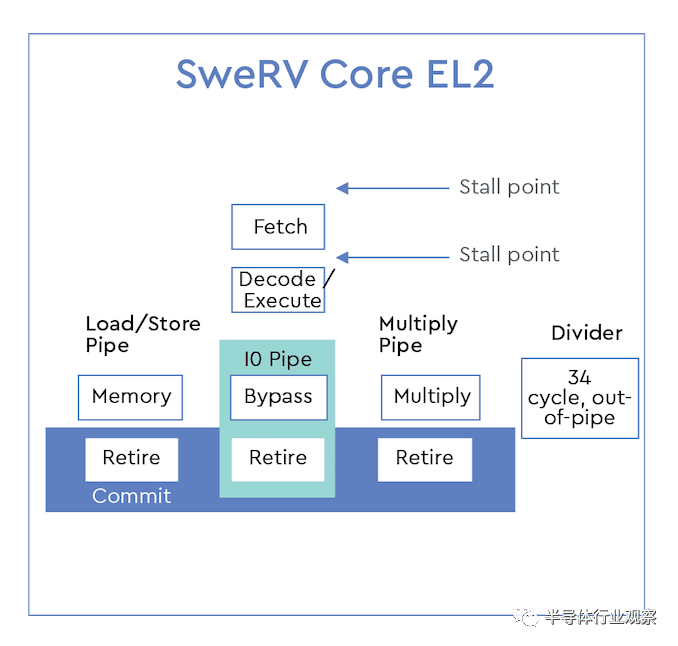

相比之下,SweRV Core EL2的目的是最小化,因为它将用于替换控制器SoC中必须尽可能小的顺序逻辑和状态机。EL2是一个32位有序内核,具有1路标量设计和四级流水线。Western Digital期望内核尺寸为0.023mm²大,并提供约3.6 CoreMarks / MHz的性能。

Western Digital表示,其所有三个SweRV内核都将“在不久的将来”用于其各种产品中,但自然不会预先宣布它们。同时,将这些核心贡献给其他人将总体上丰富RISC-V生态系统。

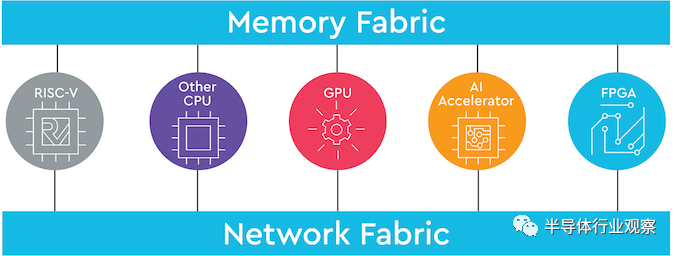

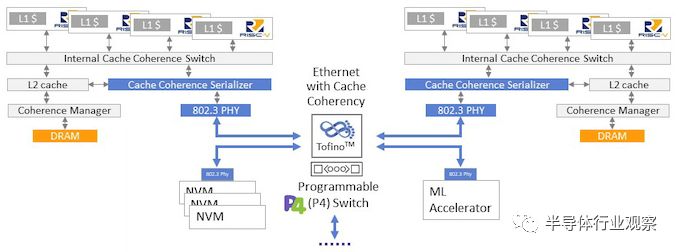

说到生态系统,西部数据展示了其第一款基于以太网兼容架构协议的OmniXtend缓存一致性存储器的硬件参考设计,这可以使芯片开发人员能够将其集成他们的设计中。最初,该体系结构可用于将持久性内存连接到CPU,但也可以集成到GPU,FPGA和机器学习加速器等组件中。该参考设计将可从Chips Alliance获得,后者还将推动OmniXtend协议的进一步开发。

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

日本半导体|AI|台积电|IC|亚马逊|RISC-V|高通|DRAM

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!