文章缘由,最近被基于RISC-V 的GD32VF103处理器疯狂刷屏…….

RISC-V 处理器采用哈佛结构,可以使用相互独立的总线来读取指令和加载/存储数据。指令代码和数据都位于相同的存储器地址空间,但在不同的地址范围。程序存储器,数据存储器,寄存器和 I/O 端口都在同一个线性的 4 GB 的地址空间之内。

注:Cortex M3:采用了ARMv7架构的,使用哈佛结构的内核。

Cortex M4:采用了ARMv7架构的,使用哈佛结构的内核。(较前者最大区别,增加了一个DSP处理功能,SIMD单指令多数据功能。其他区别请自己在实际项目开发中验) 。

RISC-V 处理器具有简单的动态分支预测、指令预取缓冲区和本地内存等多种高效微架构特点。它支持32个通用寄存器(GPRs)和用于性能/面积权衡的快速乘法器。

1.系统架构

2.存储器区域功能划分

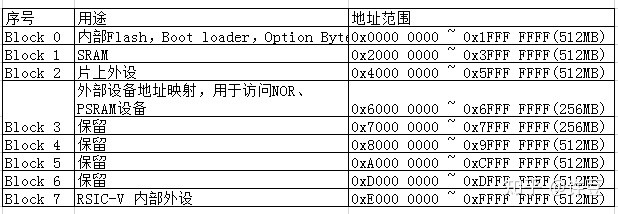

在4GB的地址空间中,RSIC-V 已经粗线条的平均分成了 8 个块,每块 512MB,每个块也都规定了用途,具体见下面表格。每个块的大小都有 512MB,显然这是非常大的,芯片厂商根据不同设计需要,都是只用了其中的一部分。

在这 8 个 Block 里面,有 3 个块非常重要,也是我们最关心的三个块。Boock0 用来设计成内部 FLASH,Block1用来设计成内部 RAM,Block2用来设计成片上的外设,下面简单的介绍下这三个 Block 里面的具体区域的功能划分。

1)存储器 Block0 内部区域功能划分

2)储存器 Block1 内部区域功能划分

Block1 用于设计片内的 SRAM。GD32VF103 内部 SRAM的大小为 32KB

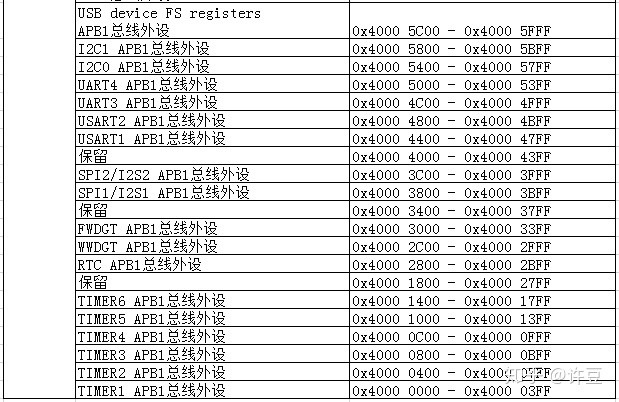

3)储存器 Block2 内部区域功能划分

Block2 用于设计片内的外设,根据外设的总线速度不同,Block 被分成了 APB和 AHB

两部分.AHB挂载高速外设(最高可到108MHz), APB挂载低速外设(APB1速度限制为54MHz,APB2可以全速运行最高可到108MHz)。

总结:从系统架构及存储器来看,对于嵌入式工程师来说,熟悉Cortex M3/M4的开发者可以快速上手,目前已有IAR,SEGGER等软件大厂开始对其支持了。

RISC-V架构与ARM CortexM系列的架构的优劣,指令集的数目,模块化可拓展性将在后续讨论。

关注公众号“嵌入式杂谈”,查看更多精彩内容!