RISC-V 能够实现“自主可控”与“普世通用”的国产处理器,中国应该拥抱此技术。

胡振波

RISC-V指令集是怎么回事就不多说了。开门见山,说说几款我接触过的开源处理器,按我接触的时间顺序来排序。

1. Rocket,BOOM

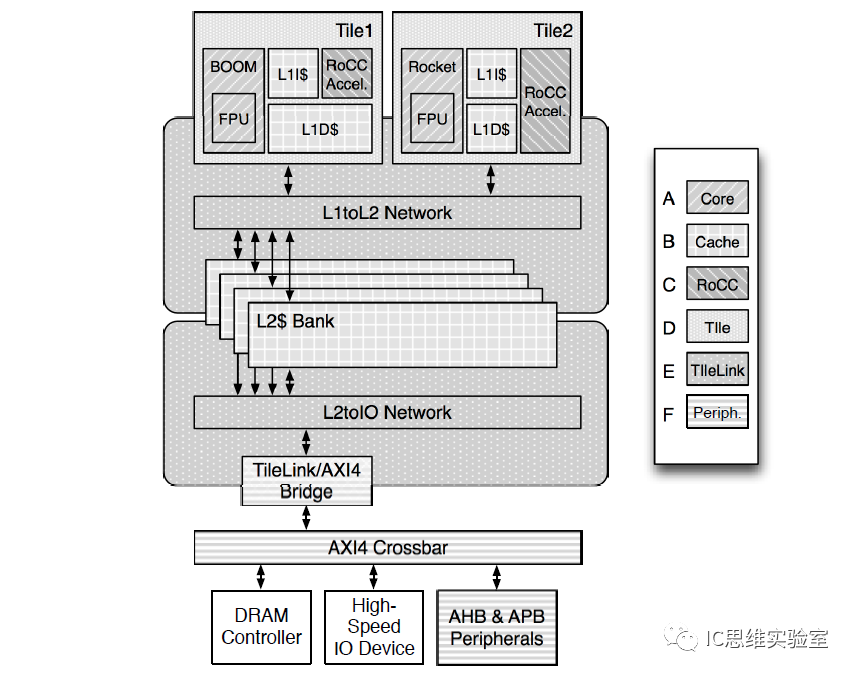

很多RISC-V开发者,无论硬件还是软件,首次接触的CPU core就是Rocket。Rocket Chip Generator可以生成包括Rocket core的一整套SoC,各种参数统统可配置。Rocket Chip是用Chisel开发的,初学者(CPU设计开发的数字前端初学者,尤其是只懂Verilog的初学者)要去看Rocket的代码还是会有些吃力的,对初学者不太友好。不过正因为其面世较早,又有Berkeley的纯正血统,粉丝众多,很多paper都是基于Rocket Chip做的,资料也很好找,但似乎没有详细的官方文档。

Rocket chip带MMU,支持操作系统,所以在上面跑Linux是没有问题的。Rocket chip使用Tilelink总线,支持缓存一致性的一款总线。支持Verilator+OpenOCD+GDB仿真。

Rocket是64位CPU core(也是今天介绍的几款处理器中唯一一款64位的),采用经典五级流水,顺序执行,单发射,还支持各种分支预测。BOOM(Berkeley Out-of-Order Machine)基于Rocket,乱序执行,BOOM有还算比较详细的文档。这两个用来学习还是很不错的。而且Rocket还是比较成熟的,基于Rocket core已经有很多ASIC产品了。只是Chisel是道坎,CPU设计还没开始学就跳进Chisel的坑里去了!

Rocket Chip github:https://github.com/chipsalliance/rocket-chip

BOOM github: https://github.com/riscv-boom/riscv-boom

一句话总结:Berkeley纯正血统,但欲学本core,必先入Chisel之坑。

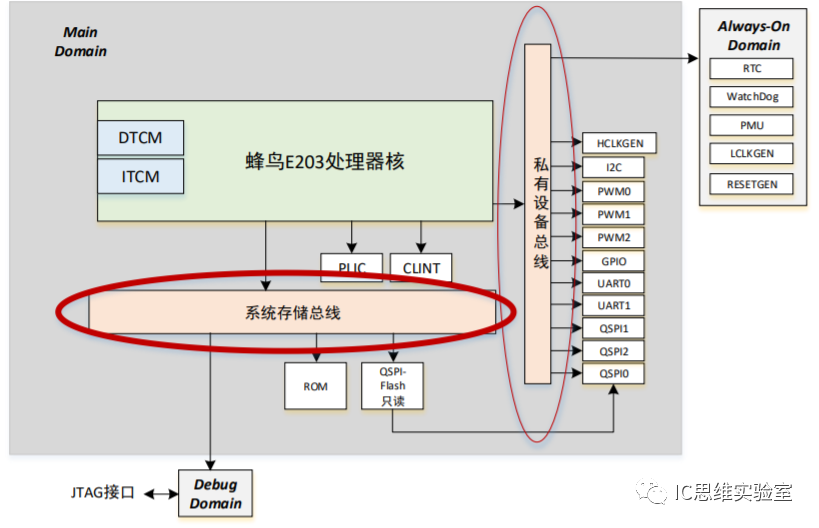

2. Hammingbird E203

蜂鸟处理器是在国内RISC-V社区大名鼎鼎的芯来科技开发的RISC-V MCU系列。E203是其开源的一款单privilege mode,两级流水(不严格说法)的MCU,主打小面积、低功耗。使用Verilog开发。麻雀虽小,五脏俱全,也包括debug module,代码严谨优美,用来学习设计没得说。官方文档不算多,但是市面上可以买到胡振波大牛写的两本书,也算是学习资料丰富了。

开源的E203在github上其实是一个SoC平台。E203使用自定义的类AXI接口,支持debug spec 0.11。唯一的缺憾是没有官方的verilator环境,如果使用verilator的话得自己搭个环境了。像我这种在家用不了商业仿真软件(也不愿意装D版)的硅农,只能用意念仿真了,目前还是看看代码,等有时间的话Port一个verilator仿真环境过去。开源蜂鸟E203支持Icarus Verilog开源仿真工具,这个仿真工具不知道还有没有人维护,就我以前使用而言,几乎只能仿纯verilog,对于很多不可综合的写法也不支持,使用非常受限,就更别提把GDB接入到仿真了。

这里值得是说一下胡振波大牛写的《手把手教你设计CPU——RISC-V处理器篇》,还是很不错的设计入门之作,里面有很多干货,是本让初学者受益良多、让熟手硅农深有共鸣的好书。另一本貌似是嵌入式开发,目前还没有拜读。

github: https://github.com/SI-RISCV/e200_opensource

一句话点评:初学者学习RISC-V处理器设计首选。

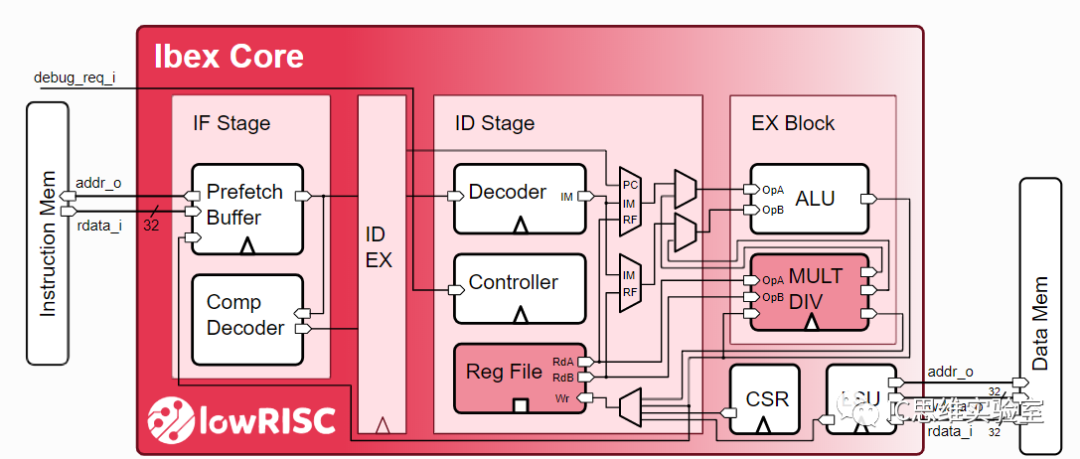

3. Ibex

提到开源RISC-V就不能不提Riscy系列了,尤其是zero-riscy,使用很广泛。Ibex是脱胎于zero-riscy的core,支持RV32IMC及一些Z系列指令,由LowRISC维护。Ibex小巧精悍,文档详实,学习资料丰富,支持verilator, 可以使用verilator+openOCD+GDB 仿真时debug。对于我这样的重度Verilator依赖者来说非常友好。

Ibex支持machine mode和user mode两种privilege mode,可以实现比单machine mode更加丰富的功能。Ibex采用system verilog开发,对于传统的IC工程师是个好消息。Ibex现在也支持了指令cache了,提高了performance,但装了cache会让core变得臃肿很多,对于学习cache controller的设计是个好事情。

Ibex使用类TLUL的自定义接口,官方的SoC是PULP。Google的OpenTitan项目也是基于Ibex。相关的设计学习资料算是相当多了。

github: https://github.com/lowRISC/ibex

文档:https://ibex-core.readthedocs.io/en/latest/introduction.html

一句话点评:啥都别说了,这么好的东西还不赶紧盘它?

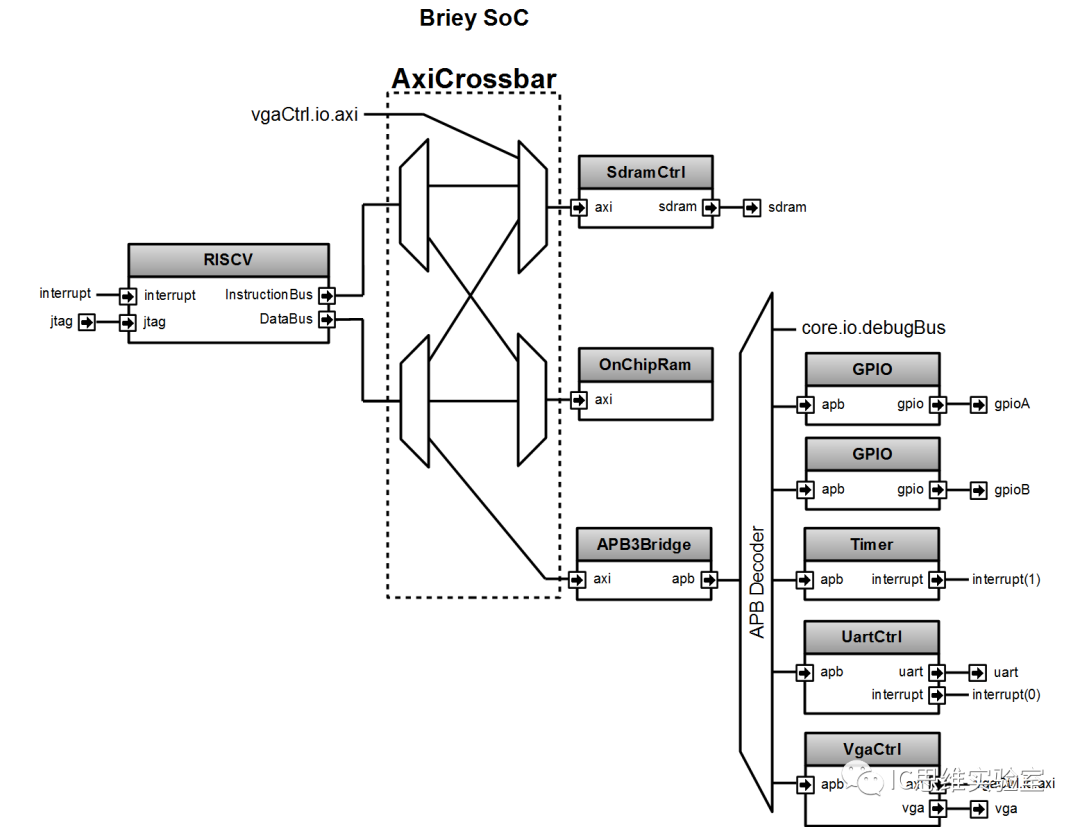

4. VexRiscv

VexRiscv可配置,可支持RV32IMCA,可配置为经典5级流水。VexRiscv使用SpinalHDL开发,类似Chisel,也是一款基于Scala的硬件建构语言。可配置MMU,所以理论上可以支持操作系统。

class VexRiscv(val config : VexRiscvConfig) extends Component with Pipeline{type T = VexRiscvimport config._//Define stagesdef newStage(): Stage = { val s = new Stage; stages += s; s }val decode = newStage()val execute = newStage()val memory = ifGen(config.withMemoryStage) (newStage())val writeBack = ifGen(config.withWriteBackStage) (newStage())//......

VexRiscv有个官方的SoC:Briey,使用AXI接口。和Rocket Chip一样,支持Verilator+OpenOCD+GDB仿真。和Rocketchip一样都是使用scala解释器sbt工具,超占内存,快把我的老爷机拖垮了。

也许是大牛都不爱写文档,VexRiscv文档很少很粗略。

github:https://github.com/SpinalHDL/VexRiscv

一句话点评:佳作,SpinalHDL代表作,需入SpinalHDL的坑。

5. SweRV EH1

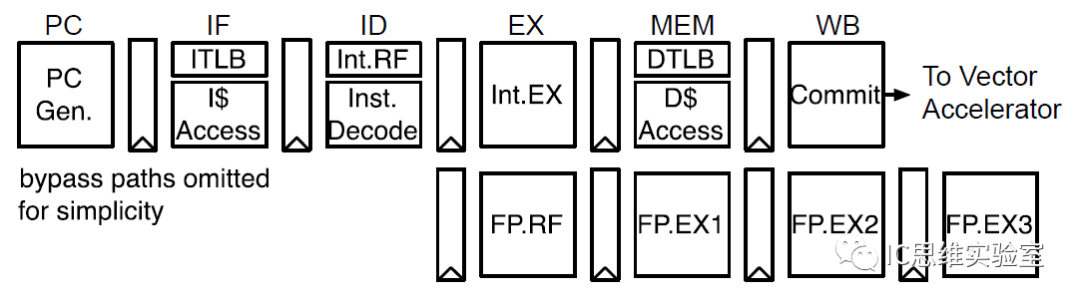

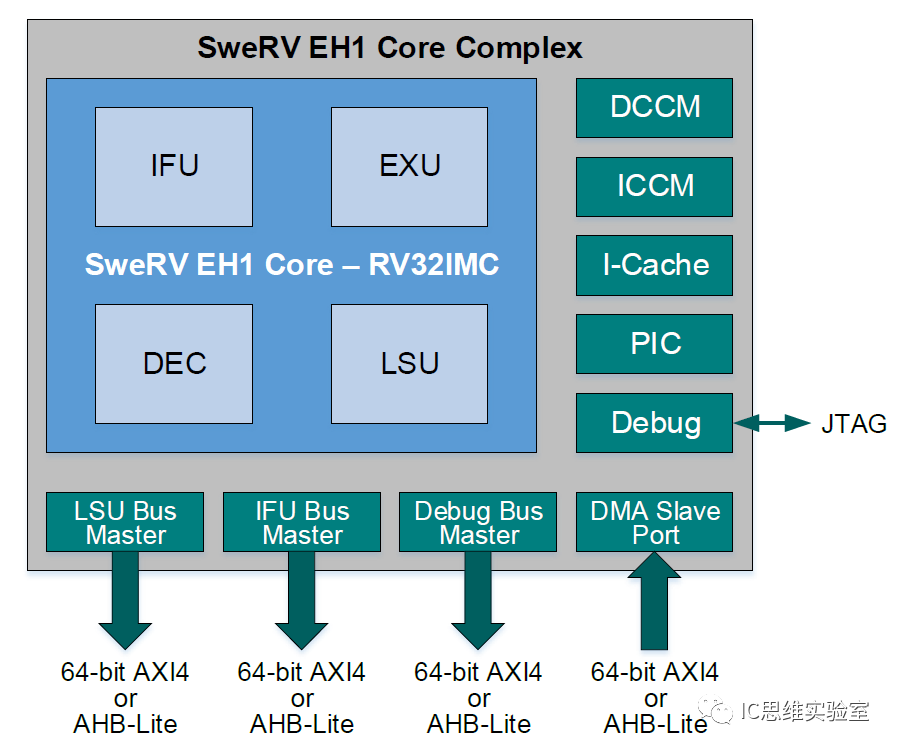

SweRV EH1是WD开发的其中一款RISC-V core,支持RV32IMC,双发射,单线程,9级流水,性能应该说是相当不错,28nm可以跑到1GHz。而且还有份详细的文档,不愧是大厂出品。

SweRV是使用Verilog/System Verilog开发,使用AXI接口,对熟悉AMBA且不想去学Chisel及Scala的同学来说是相当友好了。而且支持verilator,必须点赞。值得一提的是SweRV带指令cache,且实现了丰富的cache maintenance自定义指令,非常值得学习。

github: https://github.com/chipsalliance/Cores-SweRV

一句话点评:大厂出品,进阶学习佳作。

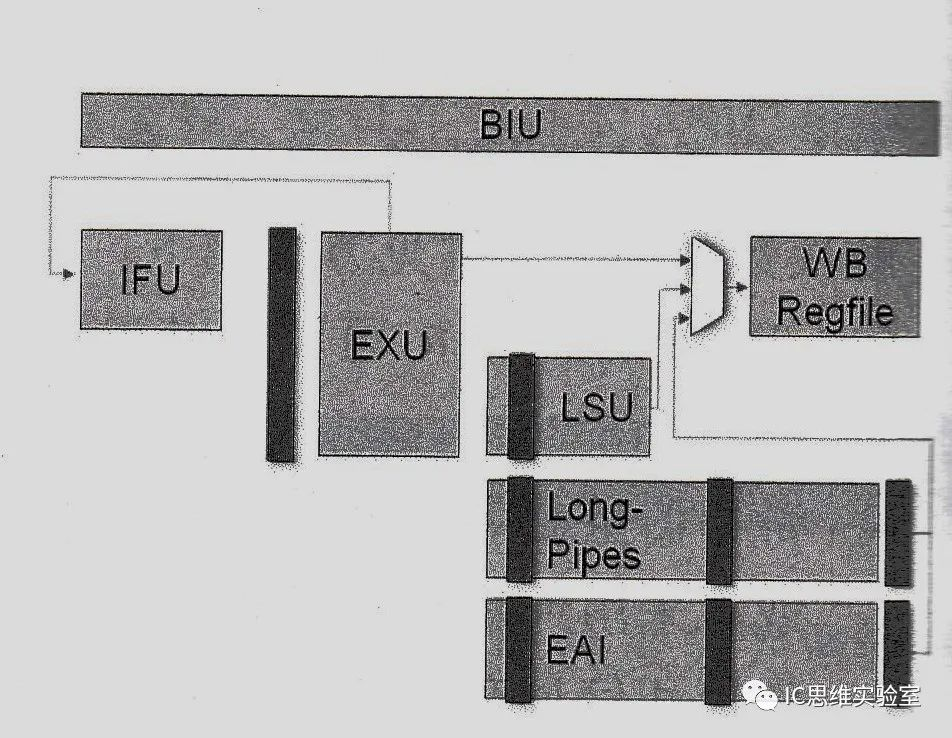

6. 无剑

听说平头哥的RISC-V处理器开源我还是很兴奋的,想仔细研究一番,但入手后有些失望。代码是刻意处理过的,注释都被去掉了,代码段的排版也非常不利于阅读,甚至有些代码是接近网表的加扰后的代码,顿时失去了兴趣。平头哥目的应该是推广这套平台,里面包括软硬件系统及SDK,从开源的程度来看,重点应该是软件。当然我是从研究学习硬件部分出发来说的,如果是使用无剑平台,包括仿真、FPGA、软件开发,应该是没有问题的。

github: https://github.com/T-head-Semi/wujian100_open

一句话点评:学习资料缺乏,代码可读性较差,不是一个理想的学习对象。