来源:电子工程世界

RISC-V指令集架构(ISA)的多功能性可以从使用该技术的5G应用的广度中看出。示例包括完整的5G基站片上系统(SoC),5G小蜂窝分布式单元(DU)SoC,针对5G无线电资源管理进行了优化的循环神经网络(RNN)IC,甚至包括RISC的手机也在开发中。

在最近的一项开发中,宣布了一种基于RISC-V参考设计的高度集成且可编程的5G调制解调器处理器。该SoC符合OpenRAN(或O-RAN)标准,适用于使用开放式软件定义内核,可互操作的无线接入网络(RAN)解决方案。与专有的基于Intel Xeon的解决方案所消耗的100W功率相比,该基于RISC-V的SoC仅消耗10W的功率,据称可将基站的总拥有成本降低多达50%。

新SoC设计的重要部分是开发了大约100条新的自定义指令,这些指令已添加到RISC-V指令集体系结构(ISA)中已经存在的向量扩展中。新指令优化了矢量扩展,以加速实现4G和5G信号处理和通信协议所需计算复杂的数学运算。

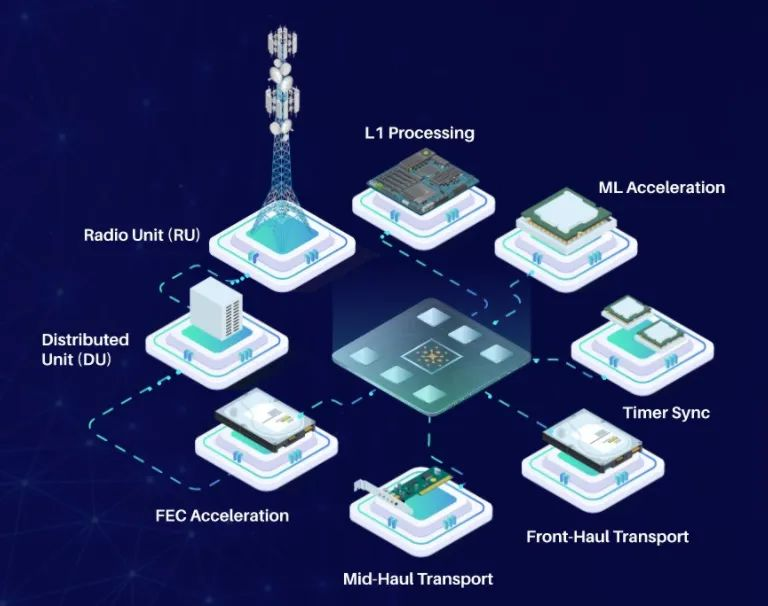

RISC-V对于高度集成的低功耗5G基站解决方案的开发至关重要。图片:EdgeQ

基站SoC使用Andes Technology的RISC-V核心许可构建的,以提供具有集成人工智能(AI)的完全开放和可编程的5G平台。最终设计扩展并定制了RISC-V指令集体系结构(ISA),以实现以前的无线基础架构解决方案无法满足的性能、功能和功耗要求。

由于SoC包括广泛的矢量处理扩展,因此它也非常适合执行AI和机器学习(ML)功能。RISC-V内核具有可用于ML活动的额外处理能力。内核在空闲时可以卸载ML活动的处理。内核甚至可以在4G / 5G和ML工作负载之间进行分区,这些工作负载是在服务质量(QoS)管理的基础上分配的。使用SoC的设计人员可以对内核进行完全C / C ++访问,从而使其比其他基站解决方案更加灵活和可编程性。除了4G / 5G基站外,预计SoC还可以在工厂自动化,工业4.0和机器人技术中找到应用。

面向5G O-RAN小型蜂窝的RISC-V

具有集成外设的AndesCore RISC-V 32位内核对于开发5G小型蜂窝分布式单元(DU)SoC至关重要。RISC-V内核的紧凑尺寸允许DU将32个内核打包到两个集群中的O-RAN SoC,从而以高达25 Gbps的线速提供灵活性和数据吞吐量,以进行数据包头处理。根据DU供应商Picocom的说法,使用小型RISC-V的群集比使用少量较大的内核更有效。这种集群化RISC-V方法支持最大的灵活性,以应对未来的5G NR标准更改,同时在要求非常苛刻的应用中提供高性能。

5G系统使用正交频分多址(OFDMA)协议。在这样的系统中,数据在大小范围从0.125到0.25 ms的时隙中传输。这些时隙中承载的流量的调度是一项关键活动。正在设计和部署高效的5G基站,以处理大量用户并支持几个独立的移动运营商。每个操作员可能需要自己的软件。因此,管理5G小区站点中的无线电资源是一个复杂的过程。

用于5G无线电资源管理的神经网络

5G新无线电的无线电资源管理(RRM)很复杂。必须最大程度地利用可用频带,尤其是在高度异构的业务(例如,微小的传感器节点与移动路由器)以及快速变化的无线电信号传播条件下。为了有意义,RRM必须在几毫秒内执行;否则,QoS可能会受到影响。5G应用场景的多样性对RRM提出了严格的要求。这些应用程序包括:自动驾驶汽车具有很高的可靠性和低延迟、视频电话和虚拟现实的高带宽、大规模物联网的机器对机器通信。

FPGA可用于处理必要的资源分配算法,以将有限的资源(例如,频带,发射功率,数据速率)有效地分配给移动客户端。但FPGA成本太高,无法用于5G网络所需的大规模密集部署中。为了满足这一需求,已经提出了针对RRM应用的具有递归神经网络(RNN)特定扩展的基于RISC-V的加速器。提出的解决方案包括硬件优化和软件优化。

这些扩展保持了与标准RISC-V ISA的向后兼容性,并且只增加了3.4%的额外面积开销,最长路径的长度不变。该解决方案非常灵活,并且支持用于各种RRM任务的多种RNN的性能改进。与基本RISC-V ISA相比,在各种RNN配置范围内,能效(10倍)和总体性能(15倍)提高了一个数量级。

RISC-V手机

以下是开发基于RISC-V的手机的三个示例。尽管这些活动不仅限于5G,但它们指出了基于RISC-V的5G手机的未来发展。

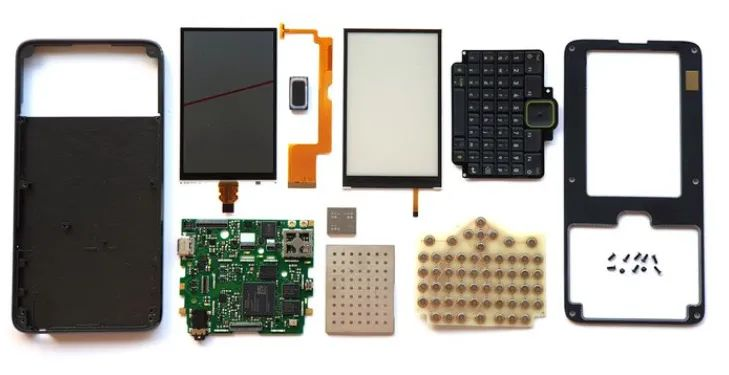

Precursor是袖珍型设备和开放式硬件开发平台,用于安全,移动的计算和通信。它包括一个内置显示器,一个物理键盘和一个内置电池,同时比普通智能手机更小,更轻。它由FPGA托管的软核片上系统(SoC)提供支持,它使开发人员可以自由检查,验证和自定义其操作的每个方面。Precursor围绕Xilinx XC7S50主片上系统(SoC)FPGA构建:一级缓存可延长电池寿命,并具有100 MHz VexRISC-V,RV32IMAC + MMU,4k L1 I / D缓存。

Precursor 开发平台组件。(图片:Precursor)

VexRISC-V基于RV32IM指令集的FPGA优化RISC-V ISA实现,该指令集不使用任何供应商特定的IP块。如在Precursor平台中使用的那样,它包括可选的MMU。

一些开发团队正在致力于在RISC-V硬件上运行Android开放源项目(AOSP)操作系统。阿里巴巴平头哥做出了一项努力,该公司已将Android 10移植到其内部RISC-V硬件中,该硬件是包含XuanTie C910内核(RISC-V 64)的SoC。

在RISC-V 64(XuanTie 910处理器)上运行的AOSP Android 10操作系统(图片:Github)

SoC集成了具有3个XuanTie C910内核(RISC-V 64)和1个GPU内核。该SoC可提供4K JPEG解码,并支持多个高速接口和外围设备以进行数据传输,包括3D图形和多媒体处理。

Debian操作已移植到RISC-V体系结构。Debian是一个安全且稳定的基于Linux的操作系统。从笔记本电脑,台式机到服务器,各种设备都在使用它。Mobian是Debian的衍生产品,该产品是为手机开发的,于2020年5月推出。PinePhone是基于Linux的基于Mobian的手机。虽然PinePhone基于ARM处理器,但Debian已移植到RISC-V为设计师开发基于Mobian的RISC-V手机打开了大门。

概括

RISC-V已在一系列5G应用中使用和开发,包括完整的5G基站片上系统(SoC),5G小蜂窝分布式单元(DU)SoC,递归神经网络(RNN) )针对5G无线电资源管理进行了优化的IC,甚至包括RISC-V内核的手机也在开发中。预计RISC-V的用途将继续扩展到越来越多的5G应用中。