我们在开始分享今天的内容之前,先思考一下,为什么 Intel 会做行业第一?

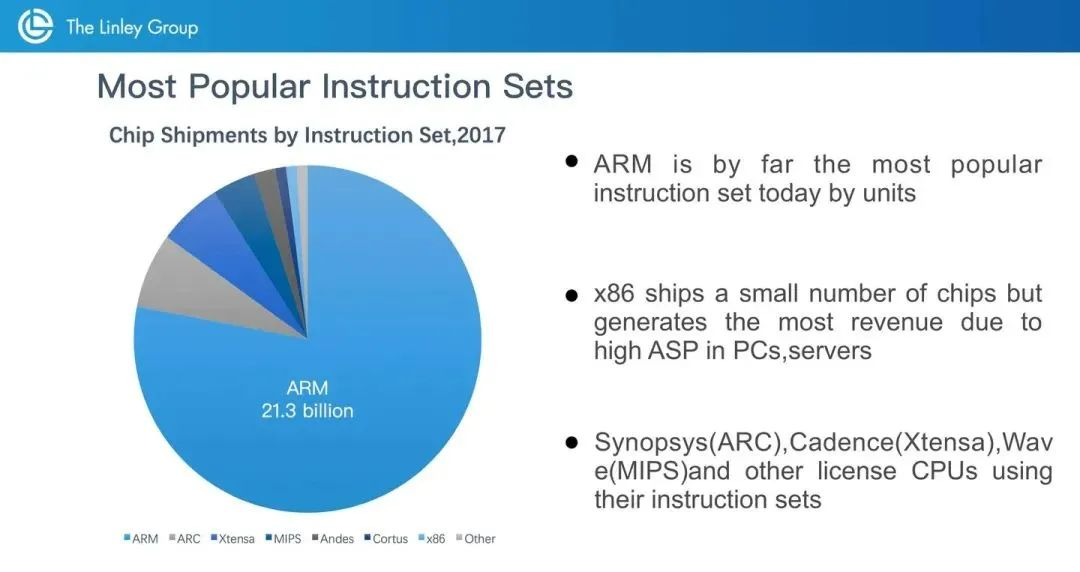

因为它有掌握成本结构的 IDM 模式,有符合摩尔定律的 Tick-Tock 策略,这些都对。但除此之外,还有一个非常重要的因素,那就是Intel掌握了x86指令集。想想为什么 AMD 能与 Intel 常年竞争?AMD 甚至在濒临破产的边缘,连总部大楼都卖了还能起死回生,重新来个 AMD YES?就是因为 AMD 和 Intel 分享了 x86 的指令集。

可能有的同学不了解什么是 IDM 模式,简单来说是指从设计、制造、封装测试到销售自有品牌IC都一手包办的半导体垂直整合型公司。

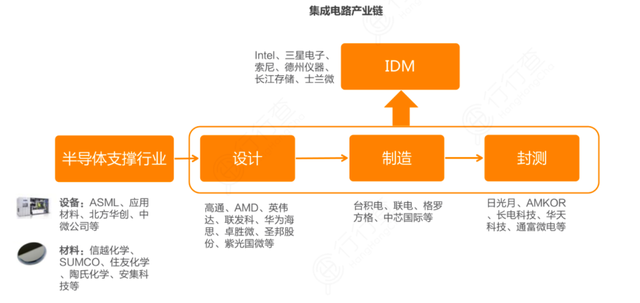

图 集成电路产业链

其模式特点是集芯片设计、芯片制造、芯片封装和测试等多个产业链环节于一身;早期多数集成电路企业采用的模式;目前仅有极少数企业能够维持。如三星,德州仪器。

图 Fabless、Foundry、OSAT、IDM模式公司典型代表

上图中的 OSAT ,全称为 Outsourced Semiconductor Assembly and Testing ,就是「外包半导体(产品)封装和测试」,是为一些 Foundry 公司做 IC 产品封装和测试的产业链环节。

Foundry,在集成电路领域是指专门负责生产、制造芯片的厂家。Foundry 原意为铸造工厂、翻砂车间、玻璃熔铸车间,从它的字面意思可以看出其与集成电路的联系,因为硅集成电路的制造也跟“玻璃”和“砂”有关。

Fabless,是 Fabrication(制造)和 less (无、没有)的组合,是指“没有制造业务、只专注于设计”的集成电路设计的一种运作模式,也用来指代未拥有芯片制造工厂的IC设计公司,经常被简称为“无晶圆厂”(晶圆是芯片硅集成电路的基础,无晶圆即代表无芯片制造);通常说的 IC design house( IC 设计公司)即为Fabless。

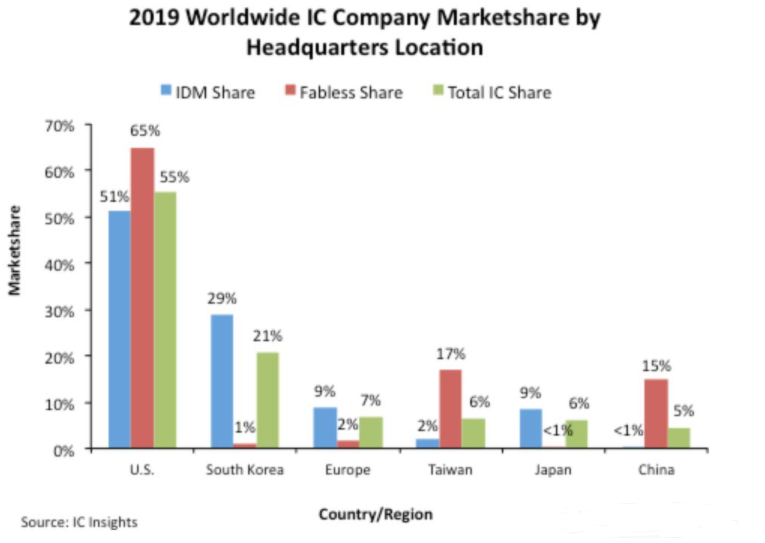

图 2019年全球头部 IC 公司市场份额占比

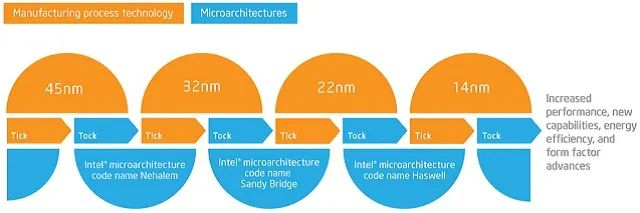

而 Tick-Tock 策略是指 Intel 从 2008 年引入的一个 CPU 研发和生产策略:每一代 CPU 都会对应 Tick 或者 Tock:

如果这代 CPU 对应 Tick,那么这一代 CPU 相比前一代将会采用升级的制造工艺,例如从 22nm 到 14nm 的制造工艺提升;

如果这代 CPU 对应 Toc ,那么这一代CPU将会进行处理器微架构升级,例如支持新功能。

图 Tick-Tock策略

今天,我们就聊聊指令集。简单聊聊 ARM 和 RISC-V 这两个在业内比较有话题性的指令集吧。

业界泰斗、ACM 和 IEEE 两院院士、2017 年图灵奖得主、 RISC-V 基金会的董事会副主席 David Patterson 给了非常通俗易懂的定义:软件通过一个专业词汇上称为指令集的东西和硬件讲话。换句话说,指令集是软硬件之间沟通的桥梁。如果在晶体管、集成电路和摩尔定律之外,再给一个重点概念,那就是指令集了。

可能你平时看新闻,看 ISA、架构、指令集这些词都混在一起用,觉得有些疑惑,其实ISA=指令集=架构,都是一个意思。而实现了一个指令集的 CPU 叫微架构。

我给你举个例子,ARMv,这是一个指令集,也是一个架构版本。ARM 的 Cortex-A72 处理器,就是一个实现了ARMv8 指令集的具体 CPU,是一个微架构。ARM 的 Cortex-A72 是一个支持 ARMv8 指令集的 CPU IP,就是一堆 RTL 代码。瑞芯微的 RK3399 芯片就是一个集成了2个 Cortex- A72 之后的芯片,是一个物理体,这个芯片支持 ARMv8 指令集。凡是支持 ARMv8 的软件,都可以在 RK3399 上运行。

指令集诞生后,CPU 厂商都开始整理、规范这些指令集,其中就包括英特尔。英特尔在它为成功的一款处理器 8086 中,开始加入大量指令集,以提高计算效率、增强 CPU 性能。与此同时,另外一种思想在悄悄萌芽。

CPU 的指令集是各种功能的集合。指令集诞生的原因是人们渴望在软件编写时更有效率,同时也符合事物发展中规范化、模块化的需求。但是,在所有指令集中,经过人们分析和统计,只有 20% 的指令集会在 80% 的场合都用到,而绝大部分 80% 的指令集只有 20% 的场合需要出现。因此便有了后来的 RISC-V 。

从指令集到硬件、软件生态

当我们说ARM的时候,我们不太关注这个拥有 6000 员工,总部在英国但被软银收购后已经成为一家日本公司的企业故事,或者是在网上可以公开看到的那本 5000 多页的 [ARMv8指令集手册]。我们更多提到的是硬件侧高通的骁龙、联发科的天玑、华为的麒麟、三星的 Galaxy、AWS 的 Graviton、苹果的全家桶,和软件侧的 Android、iOS、Red Hat、Ubuntu、SUSE、麒麟 OS,等等,它们都在 ARM 的生态系统里。我们关注的是整个 ARM 生态系统。

类似的,我们在说 x86 的时候,也不仅仅指的是 Intel 和 AMD ,还有在 x86 生态系统里的微软、Linux、Oracle、SAP 等等。但是 x86,并不是一个公开授权的指令集,虽然并不仅仅有 Intel 和 AMD 两家,但是对于新入局者来说,做 x86 指令集的机会几乎微乎其微。相对来说,ARM 和 RISC-V 都是开放授权的指令集。ARM 是商业授权指令集,RISC-V 是开源的指令集。至于 CPU 核,也就是微架构,两家都是商业授权模式,就是要付费的。

图 2017年统计最受欢迎的指令集

当年 Intel 推出 x86 指令集的时候,已是万人大厂,还拿下了 PC 这个关键市场,而彼时微软才刚刚创立,不足 10 人,因此这是一个先建硬件再建软件的历程。而 ARM 是靠着自己的灵活授权模式,搭着当年德州仪器的大船杀入到手机市场,并在功能机年代拿下手机这个关键市场的。然后先有诺基亚的手机操作系统塞班,然后再有的 Android。

在移动互联网时代,ARM 也是运气好,Intel 没有答应苹果的定制要求,因此苹果就选了 ARM这个现成的 CPU IP,也采用了既有的指令集,再搭建 iOS 系统。因此 ARM 赶上的是硬件统一,软件分裂,然后对齐到硬件上的过程。

那么开始于 2010 年的 RISC-V 呢?我推荐你读一下中国科学院计算技术研究所包云岗老师的解读和介绍。

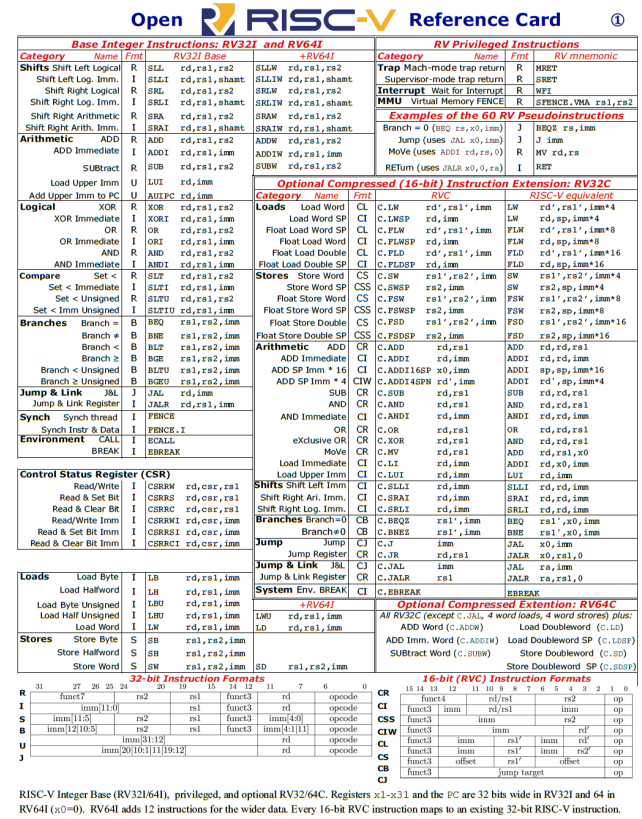

图 RISC-V-Reader-Chinese-v2p1 Reference Card

包老师团队翻译了 RISC-V 手册,副标题是《一本开源指令集的指南》(http://staff.ustc.edu.cn/~xhzhou/reference/RISC-V-Reader-Chinese-v2p1.pdf)。

RISC-V 诞生于美国 UC Berkeley 大学,最初是个开放为教学服务的指令集。但 RISC-V 因为有着精简、高效、低能耗、模块化、可拓展、免费开放、无历史负累低效指令等优势,很快就出圈了,因此 RISC-V 团队在认识到它的价值之后,就决定将之推出市场进行商业化探索。

RISC-V 架构秉承简单的设计哲学,完全抛弃历史包袱,从轻上路,借助计算机体系结构,经过多年的发展已经成为比较成熟的技术。RISC-V 基础指令集则只有 40 多条,加上其他的模块化扩展指令总共几十条指令。RISC-V 的规范文档仅有 145 页,而“特权架构文档”这样重要的内容,篇幅也仅为91页。

如果说 ARM 借助IP授权的商业模式,降低了 CPU 设计难度,让信息技术世界进入泛处理器时代,那么 RISC-V 就是以免费开放的开源指令集模式,降低了 CPU IP的设计门槛,让芯片行业进入到一个满是 CPU IP 的时代。RISC-V 目前已经有 200 多家成员,你可以看这张大厂 logo 云集图片,这张图来自 RISC-V 基金会。

图 RISC-V 基金会成员

不过所有的技术或者商业模式优势,最终还是要转化成商业成功。目前所有参与 RISC-V 的企业,其实还是小公司居多,或者是大公司的小项目有涉及,还没有特别赚钱的。

在早期, ARM 是 RISC 的代表,而 x86 是 CISC 代表。传统观念中, RISC 指令更精简效率更高,但今天的 CPU 这观念已经很不准确了。大体上来说, RISC 概念提出之初,相比于 CISC 的区别在三个方面:

指令数量更少而且功能更简单。实现指令消耗的晶体管更少;单一指令的执行时间更短,更容易提高 CPU 工作频率;

没有内存操作数。相同功能的单一CISC指令所实现的功能需要更多的RISC指令实现,最起码要分拆为从内存加载数据和执行相同计算的RISC指令这样的两条RISC指令;

定长指令,从指令数据流中截取、提取指令更简单。

RISC 的1、3 两个优势,是建立在半导体集成电路普及,晶体管工作频率不断提升,存储器成本不断下降的基础上的。

在半导体集成电路尚未流行,电路基础原件是各种电子管,常见型号的 CPU 每秒只能处理不到1百万条指令,不到 1MB 容量内存的计算机采购成本还需要上百万美金的那个年代,很显然 CISC 是性能更高而且成本更低的解决方案。

但到了今天,x86 CPU,内部都已经把传统的 x86 指令分解为类 RISC 的微操作(Micro Operation,uOP),这些 uOP ,都不支持内存操作数( LOAD/STORE 这样的内存操作指令,地址其实是即时操作数),第二点的区别已经没有了。

今天的 x86,对很多使用频率低且功能复杂的指令,某个角度来说其实已经被放弃了。为了兼容性,用一个叫微码序列器(microcode sequencer)的机制来对这些指令进行解码。不同于前面提到的内存操作指令分解为load微操作、同功能的微操作、 store 微操作,这类指令并没有对应的同功能微操作,而是用多条简单功能的 uOP 组合去实现单条指令的功能。

所以,今天的CISC和RISC,第一点的差别也几乎可以忽略了。

而第三点的定长指令,以及带来的解码简单,则是成为今天RISC区别于CISC的最大优势。CISC 的变长指令,导致 CPU 的解码器在分析完毕一条指令前,无法确定下一条指令的起始地址。因此在一个时钟周期内能解码完毕的指令数量很难提升。

目前 x86 两家 CPU 厂家,最高解码数量分别是 Intel 的 5 条指令和 AMD 的 4 条指令(不是说 Intel 的解码性能一定更好,因为 Intel 是 1+4 ,5 条指令只能有一条复杂指令,其它 4 条必须是有对应 uOP 的简单指令;而 AMD 的可以 4 条全部是复杂指令)。

RISC 因为是定长指令,因此理论上可以有任意多个解码器对任意多条指令进行解码。当然,这是要付出其它代价的。首先是更多的解码器需要更多的晶体管来实现。其次是解码出来的大量 uOP 需要更宽的超流水线、更多的执行单元处理,这都会耗费更多晶体管。再次是指令间一旦出现数据数据依赖,必须有更多条目的乱序缓冲区 ( Re-Order Buffer,ROB ) 来临时存放堵塞的 uOP 。最后则是需要更复杂的乱序执行算法,对更大量的 uOP 进行分析,以决定哪些指令可以提前执行。

因此,RISC 可以做出架构很宽的 CPU ,例如 Apple Silicon 的 A 系列及从 A 系列衍生的 M1,IBM 4/8 SMT的 POWER ,这些 CPU 单个核心的 IPC 都比 CISC 的 x86 强很多。

CISC 借鉴 RISC 的思想,让自己获得了新生。RISC 指令简单并且相对固定,处理快速,在设计上甚至可以使用更长的流水线来达到高频率,并终获得更优秀的效能。但 RISC 的主要问题在于指令集简单,因此在处理一些比较复杂的应用时,存储器需要读入的指令总数耗费时间更多,部分场合下性能表现不理想也是 RISC 的硬伤。因此,在 RISC 的发展中, RISC 也在逐渐注入 CISC 的思想。比如紧跟时代加入一些新的指令集,更进一步优化内部架构等。

RISC 发展到现在,指令也逐渐增多,浮点计算等重要性能也日益强大。不但逐渐增强浮点计算性能、新增专门的浮点指令,还在现有的基础上开展高性能 ARM 处理器的发展,以增强应对市场变化特别是对 x86 处理器竞争的能力。

从目前 CPU 的发展来看,无论是 ARM 、 x86、还是 RISC-V ,除了努力巩固自己的性能优势,加强产品的性能外,还积极吸取对方产品的特色,取长补短,期望有所突破。不过无论如何,未来肯定在朝着高性能、低功耗的方向发展。

移动计算大潮已经来临,竞争日趋激烈。但说到底就是性能功耗比的竞争,谁能在低功耗下提供高性能,谁就有希望获得成功。未来的处理器,功耗将更低,效能会更高。

那什么算是商业成功呢?

依据我的经验以及总结 ARM 成功的历史,我列了三条 RISC-V 作为指令集的成功标志:

最新工艺的 SoC 量产

有软件支持的里程碑

支持杀手级应用或者说核心市场的 25% 市场份额

我觉得达到任意一个即可,当然最终肯定都会有,但是成功的起点是拿下其中之一。

看到这里,你如果对RISC-V仍然感兴趣,我建议你去读一下 John Hennessy 和 David Patterson 这两位图灵奖获得者,在 2019 年发表的文章《计算机架构的新黄金时代》(中文版(吴进:2018年图灵讲座:计算机体系结构的黄金时代),你可能会对 RISC-V 有一个全新的认识。如果把它当通用 CPU,它生得晚了,可是如果把它当作领域专用架构 DSA(Domain Specific Architecture),这种模块化的设计,非常有价值,而且它是先立标准、开源开放,这样碎片化的生态累积起来更灵活更高效,反而更有机会做大。

但是我想说生态始终还是要统一的,要有人掌握灵活和标准之间的平衡,否则软件投资无法得到保障,最终还是一盘散沙。

最后,我用一张 1992 年微处理器论坛的老照片作为结尾。指令集并不算一个特别有技术难度的项目,1960 年代,IBM 的每台计算机都有自己的指令集和工具。1992 年,那张图上也是有满满的指令集。都说我们芯片这行做公司容易死,但其实图里的公司,还是剩下了大半,而指令集就剩下两个了。

图 1992年的指令集

计算机指令集的发展,是“长坡滚雪球”,要有核心,不能碎,或者说生态不能分裂,还要持续稳定地不停地滚动,即保持演进,与时俱进。当然还要这个“坡”够长够大,才有后期的如雪山压顶之势,拿到容量够大的核心市场。