如何打造一个RISC-V CPU?

自制处理器也可以使用热门新技术。

很多人都有一种想要打造自己的CPU的渴望。我们正在思考我们认识之中隐藏着的一条鸿沟,这就是“逻辑门和触发器如何单独工作”与“机器代码如何控制一个完全组装的处理器”之间的差距。在硬件电路开始跟随软件不断变化的魔法世界里到底发生了什么。

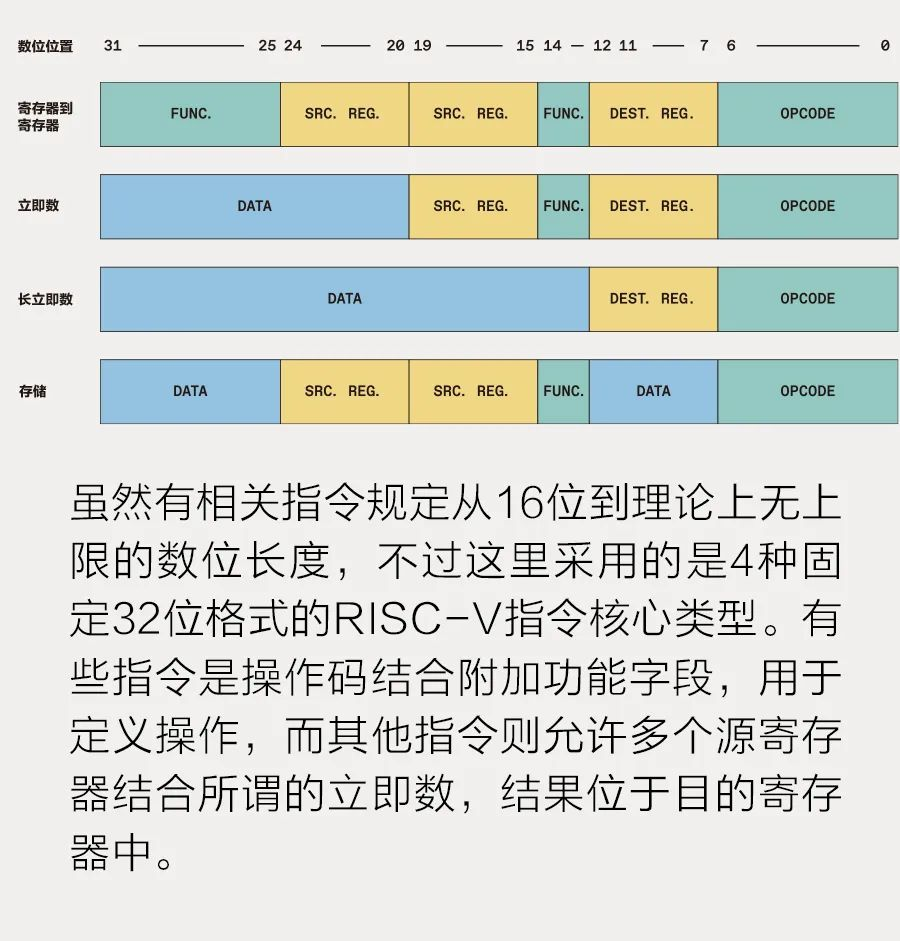

事实上,这种渴望很折磨人。人们想要把CPU组装起来并看到(或听到)它运行,如今已有可用的商业套件,网络上还有很多自制的4位或8位CPU的结构,它们都是20世纪70年代的工程师熟悉的结构。我知道这些是因为我自己打造过一个CPU。不过我也开始疑惑:我自己能打造一个采用最新技术的CPU吗?我自己能设计全兼容32位RISC-V中央处理器吗?RISC-V是一种已有11年历史的开源架构,现在这种架构正在撼动被X86和ARM CPU架构所统治的世界。罗伯特•巴鲁克(Robert Baruch)两年前开展了一个类似的项目,不过目前他还没有完成他的处理器,部分原因是他必须不断地重新设计自己早期打造的组件,使其能够满足不断发展的设计需求。他的工作让我开始留意RISC-V的可能性。与之不同,我从在Logisim Evolu-tion中构建完整设计开始,我把它命名为“菠萝一号”(Pineapple One)。Logisim Evolution是一种逻辑电路模拟器。在参考了官方RISC-V手册以及大卫•帕特森(David Patterson)和约翰•亨尼斯(John Hennessy)的第一版《计算机组织与设计(RISC-V版)》(Computer Organization and Design,爱思唯尔出版社,2017年)并突破Logisim的外部界限后,我在6个月内制造了“菠萝一号”的可运行模拟程序,符合RISC-V CPU的基本要求。安装并启用RISC-V架构令我感到很惊讶,因为与我以前自制CPU中所用的常规复杂指令集相比,这种架构非常合理。冗余消失了,处理器的寄存器更灵活。寄存器是存储CPU工作记忆的暂存器。此外,RISC-V显而易见的模块设计也是一个优点,这样我知道每个模块实现什么功能。我的目标是按自己的方式来设计每个模块,同时确保其能够按照RISC-V标准来运行。(这表明我的CPU是32位的,因为RISC-V指令的长度至少是32位。)

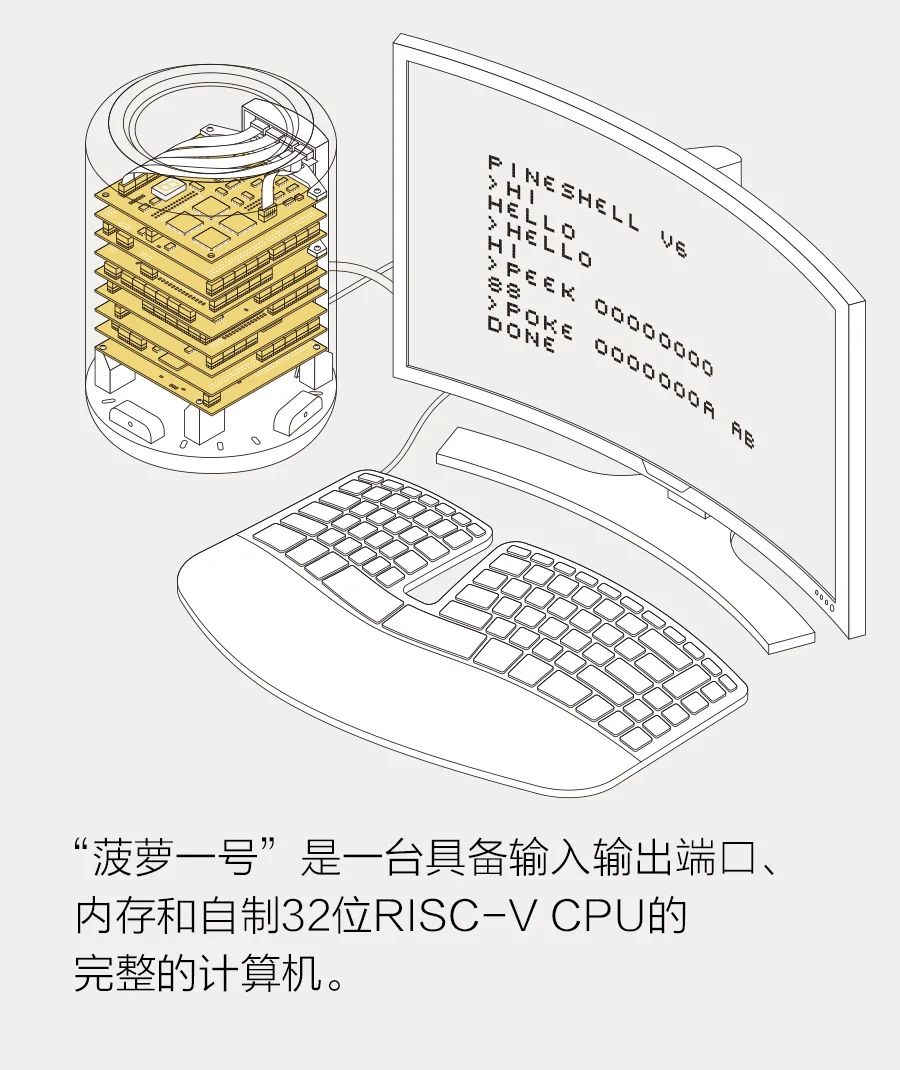

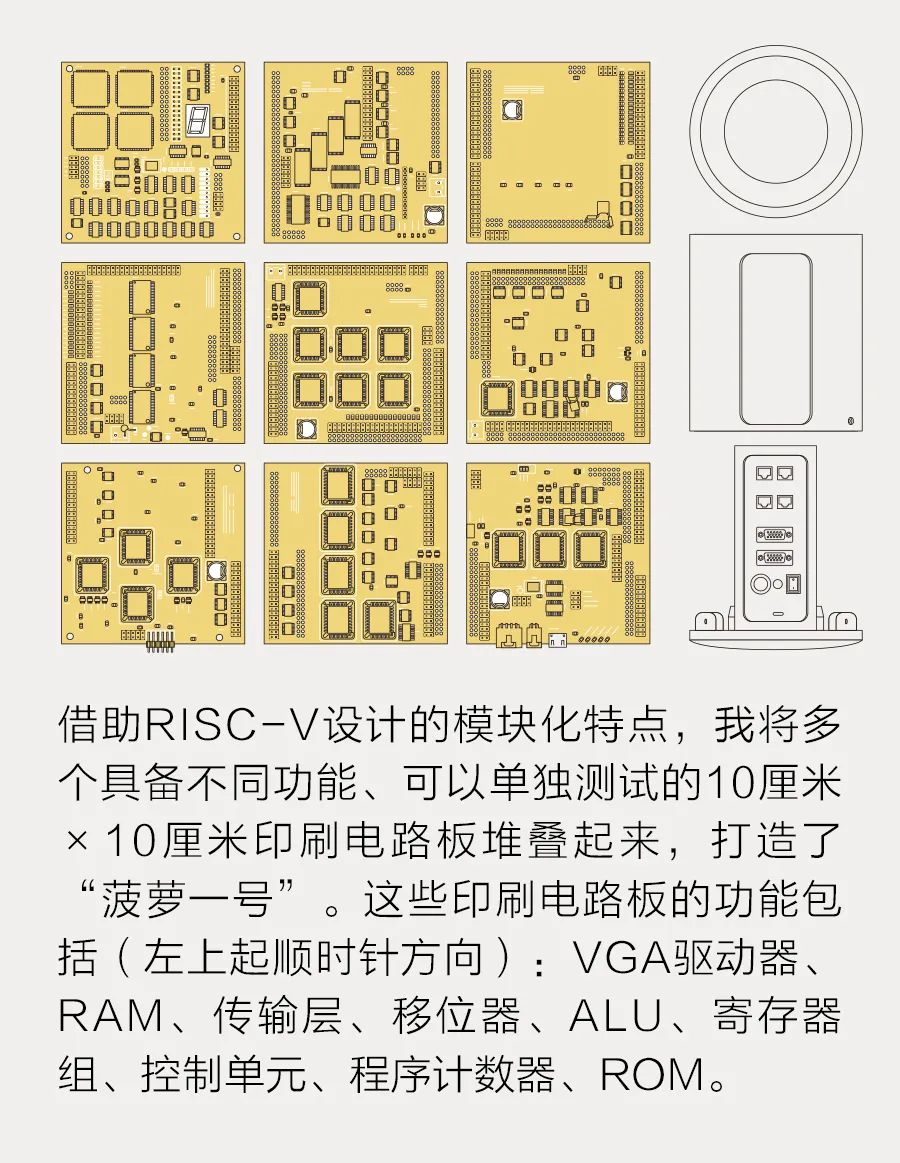

实际上,“菠萝一号”由8个正方形的印刷电路板垂直叠加组成,每块侧边长约为10厘米,外加一个可处理视频图形阵列(VGA)显示接口的卡。总共使用了230多个集成电路,大多数是74HCT系列逻辑芯片。我面临的最大挑战是安装一个桶形移位器,这是一种能够在寄存器内可控移动数据位的电路。首先,我尝试了一种快速实现的方法,它需要80多个组件,但我尽己所能也无法将其恰当地放在印刷电路板上。于是我采用了一种需要较少组件的方法,这种方法实际上会在移位器完成移动前暂停CPU其他部分的操作。由于“菠萝一号”与单芯片CPU相比有着更长的线路,因此我还努力地管理寄生电容和阻抗,处置一些古怪的现象。我对每一块印刷电路板进行了测试,用Arduino微控制器来模拟来自计算机其他部分的输入,同时监测输出的正确性。我还3D打印了一个漂亮的外壳,将这些印刷电路板和输入输出接口纳入其中,这样我就能够直接将键盘和VGA显示器与“菠萝一号”连接起来。此外,它还有4个多用途输入输出端口,其中两个是8位输入端口,两个是输出端口。

我的朋友扬•维基达尔(Jan Vykydal)帮我设置了一个兼容RISC-V的编译器,我用C语言编写了系统软件和demo程序。这个编译器能够产生机器代码,我使用了Python脚本将代码写入CPU的内存中。尽管“菠萝一号”的运行速度只有500千赫,不过这种速度足够实时玩《贪吃蛇》这种简单的电脑游戏了。其512千字节的程序内存和512千字节的RAM也足够使用了。

最后,我还想对这台处理器进行一下升级,使其能够运行更复杂的程序。我还想要添加更多的扩展卡,例如声卡。如需有关该项目的原理图和材料清单,可以通过Hackaday获取。我希望最终能为有兴趣理解当代CPU设计的人提供一个套件。

*免责声明:以上内容仅供交和流学习之用。如有任何疑问或异议,请留言与我们联系。