近日,兆松科技与芯来科技共同宣布达成战略合作,携手促进RISC-V产业与生态发展。

芯来科技作为国内领先的RISC-V CPU IP和解决方案供应商,其CPU IP应用领域广泛,覆盖从低功耗到高性能的各种应用需求。兆松科技近期发布的ZCC工具链已全面支持芯来科技RISC-V处理器内核,包括芯来科技自定义扩展指令集Xxldsp(n1/n2/n3) 和 Xxlcz,为芯来科技及其合作伙伴提供更多的选择,以达到更高的代码密度和性能,从而满足更加广泛的市场应用需求。

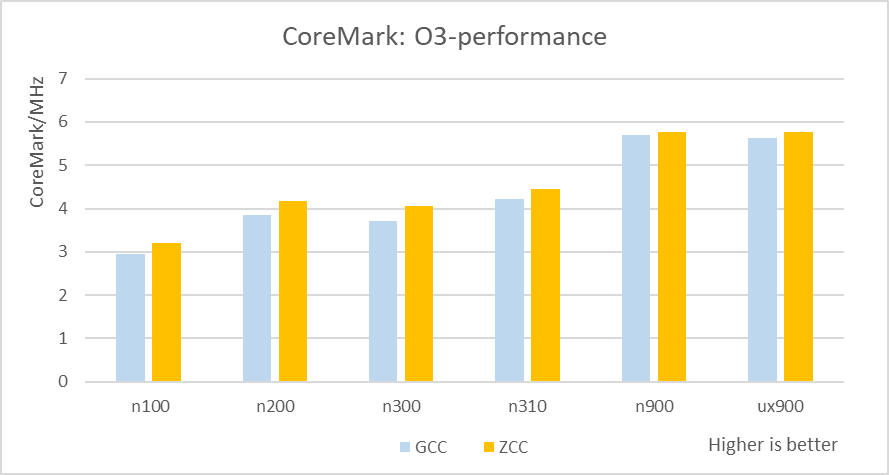

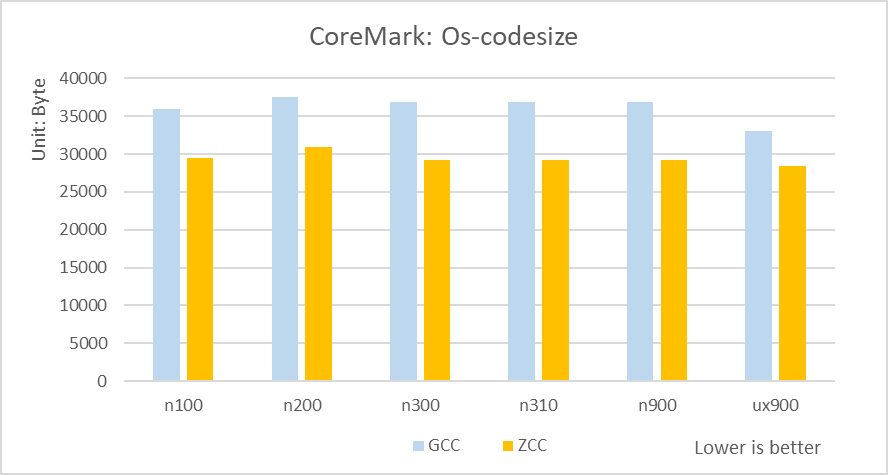

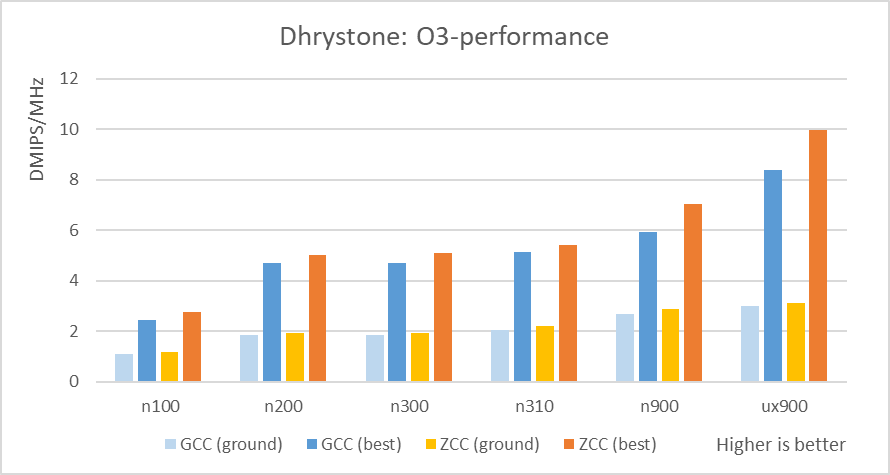

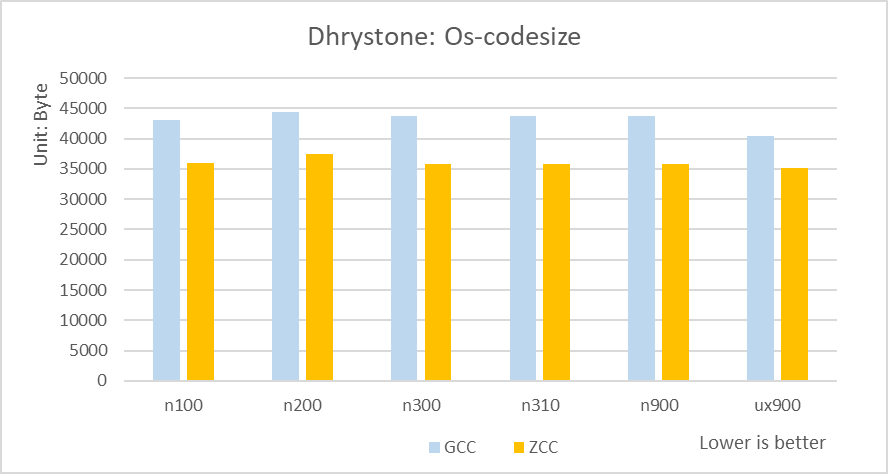

根据Benchmark测试结果,ZCC工具链在芯来科技的全系列RISC-V处理器内核上均能实现不同程度的性能提升,其中CoreMark最高实现9.38%性能提升(O3优化),以及最高20.78%代码密度优化(Os优化)。

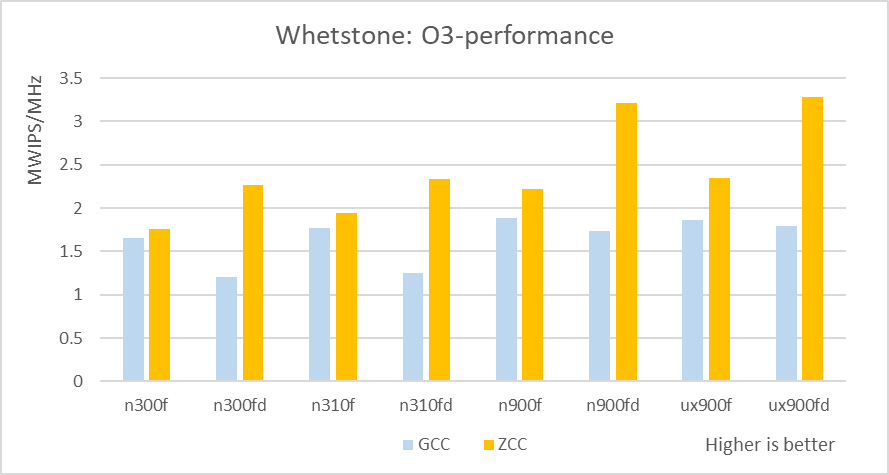

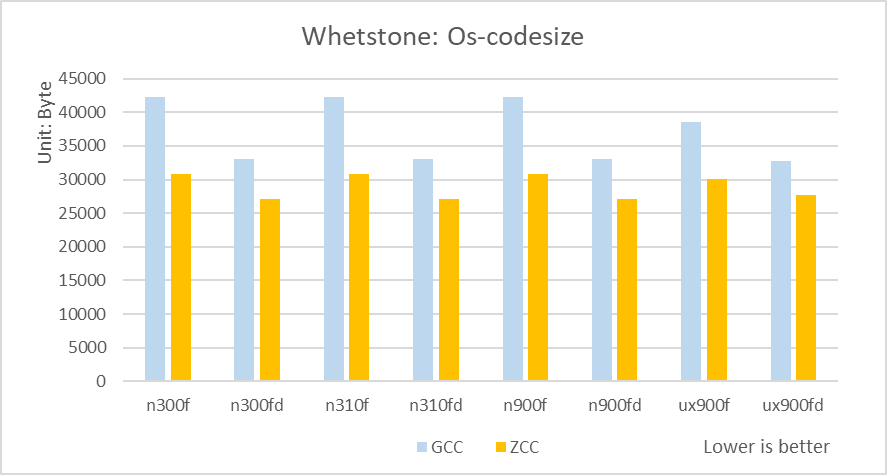

Whetstone单精度浮点测试结果最高提升25.90%;双精度浮点测试结果全面提升80%以上,最高实现88.52%性能提升(O3优化)。Whetstone代码密度优化最高达26.97%(Os优化)。

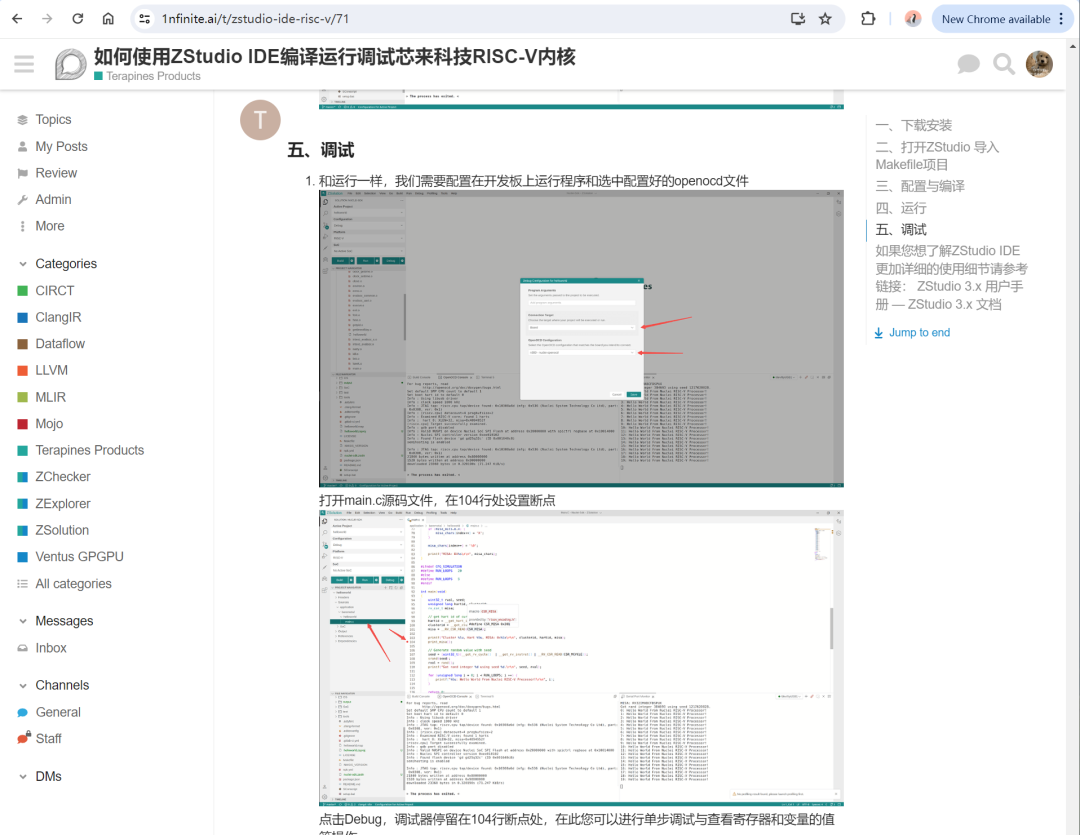

目前,兆松科技的ZStudio IDE已支持芯来科技SDK的导入,极大方便用户在ZStudio中针对芯来RISC-V处理器进行嵌入式开发,具体使用方法请参考1nfinite社区教程贴:

https://1nfinite.ai/t/zstudio-ide-risc-v/71

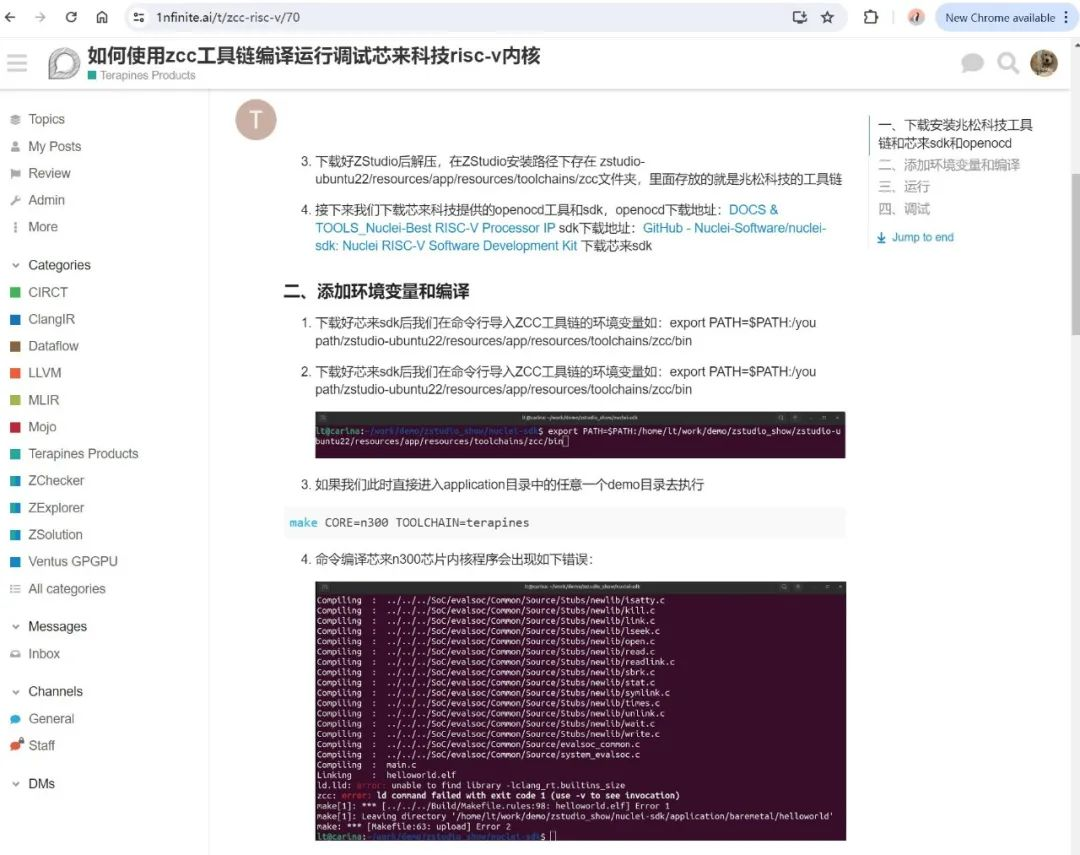

同时,芯来科技的Nuclei SDK已添加ZCC工具链的完整支持,用户也可直接基于Nuclei SDK进行开发,具体方法请参考1nfinite社区教程贴:

https://1nfinite.ai/t/nuclei-sdk/70

1nfinite 社区教程贴

为更加方便用户的使用,芯来科技将在下一版本的Nuclei Studio中集成ZCC工具链。

此次战略合作的建立发挥了双方各自的优势,高性能RISC-V IP结合高性能RISC-V工具链,为客户带来更好选择和更强的市场竞争力。兆松科技与芯来科技的紧密合作将为RISC-V用户提供更加全面、高效的解决方案,为RISC-V架构在各个应用领域的推广和发展注入新的动力。

▼往期精彩回顾▼

芯来发布NI系列内核,NI900矢量宽度可达512/1024位

芯来携手西门子EDA,推进RV CPU Trace完整解决方案

芯来携手战略伙伴为RISC-V CPU IP提升DFT可测试性设计

亮相国际舞台 | 芯来RISC-V CPU IP北美峰会引关注