RISC-V International社区在过去的一年取得了令人印象深刻的增长和技术进步。据介绍,RISC-V International的会员数量同比增长超过26%,在70个国家/地区拥有超过3180名会员。如今,市场上有超过100亿个RISC-V 核心,全球有数万名工程师致力于RISC-V计划。

「大热的RISC-V:全球出货突破100亿个,会员同比增长26%」——半导体行业观察

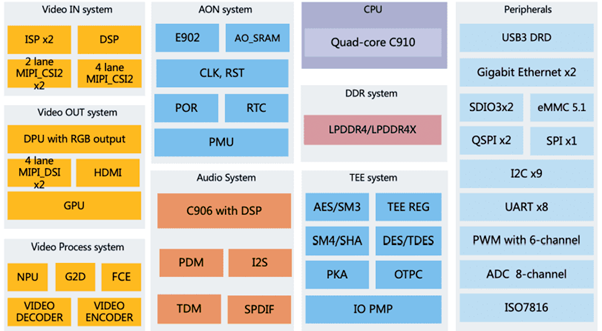

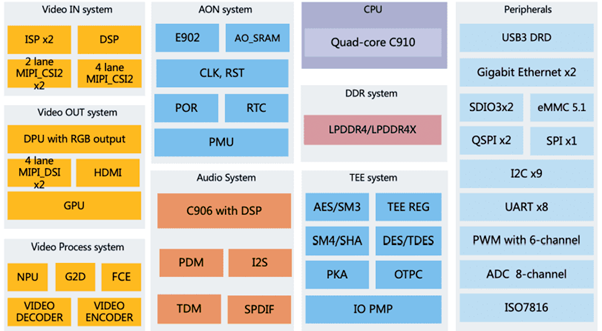

矽速首发高性能RISC-V SOM:LicheeModule 4A(简称LM4A),这是首款超越主流ARM Cortex-A72性能的RISC-V量产板卡!LM4A基于平头哥曳影1520原型芯片,是一款多核异构的高性能RISC-V SoC。

它包含四核玄铁C910(RV64GCV),主频最高可达2.5GHz;一个玄铁C906(RV64GCV)内核的DSP协处理器,主频可达800MHz;一个低功耗处理器核玄铁E902,和GPU,NPU等。「矽速首发高性能RISC-V SOM: LM4A」

图片来源:Sipped

——Sipeed

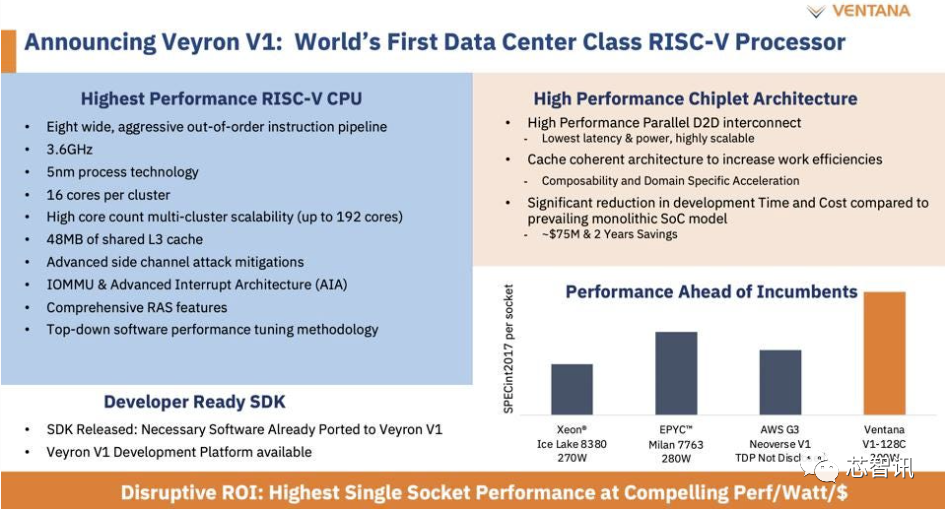

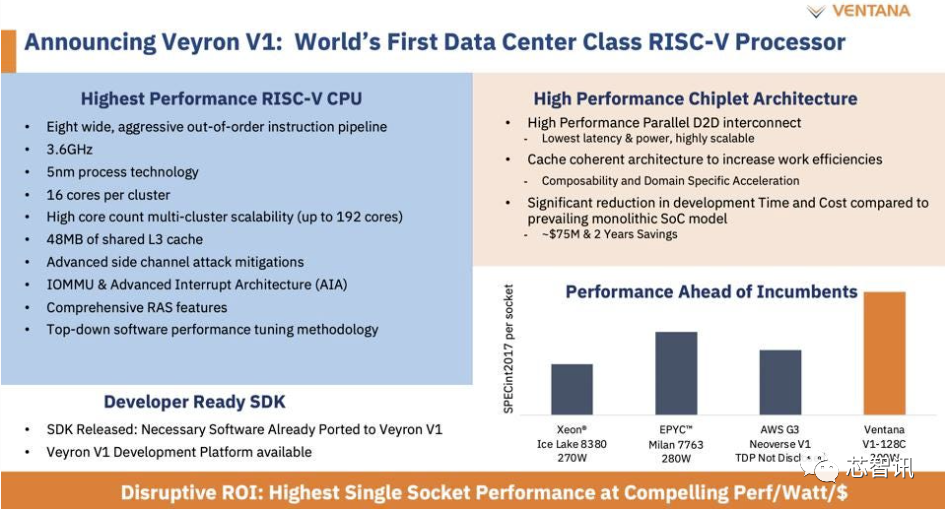

12月12日,芯片初创企业Ventana Microsystems公司在RISC-V峰会上发布了全球首款面向服务器的CPU——Veyron V1。

据介绍,Veyron V1采用先进的5nm制程工艺,基于Ventana自研的高性能RISC-V内核,8流水线设计,支持乱序执行,主频高达3.6GHz,每个集群最多16个内核,多集群最多可扩展至192核,拥有48MB共享三级缓存,拥有高级侧信道攻击缓解措施、IOMMU和高级中断架构(AIA)、支持全面的RAS功能、自上而下的软件性能调整方法,可以满足数据中心的各种需求。「RISC-V杀向服务器市场!5nm制程、最高192核,性能超AMD EPYC 7763!」

图片来源:芯智讯

为了进一步推动国内RISC-V相关的技术发展和生态建设,促进学术交流,中国科学院软件研究所拟定于2023年6月份举办第三届RISC-V技术及生态研讨会(RVTE2023)。会议由中国科学院软件研究所主办,聚焦于RISC-V相关的原创性研究成果,包括软件技术、系统应用及生态建设等。现将有关征文事项通知如下,欢迎大家踊跃投稿。

http://www.is.cas.cn/xshd2016/xshy2016/202212/t20221205_6566277.html——中国科学院软件研究所

集微网消息,据金融时报报道,Arm确定美国和英国不会批准向中国出口技术的许可,阿里巴巴将无法购买一些最先进的芯片设计。因中国公司同其它国家公司一样大多采用Arm的设计来构建从智能手机到服务器的设备,因此Arm被认为很容易受到美国针对中国的出口管制措施的影响。

「Arm确认无法向中国出口先进芯片设计 阿里等中企将受影响」https://www.laoyaoba.com/html/share/news?source=app_ios_3.5.8&news_id=842058——爱集微

System Level Solutions(SLS)公司是一家提供各种接口、通信协议、内存控制器、处理器等集成方案提供商。SLS近日宣布,其USB主机和设备控制器IP已经适配了Cyclone 10 GX FPGA开发板。该开发板是Intel®Pathfinder计划中最近新增的一块支持板。

「Intel Pathfinder计划中适用于RISC-V平台的USB IP」https://www.design-reuse.com/news/53120/usb-ip-cores-intel-pathfinder-risc-v-platform.html——Design & Reuse

Intel®Pathfinder近日公布了围绕着RISC-V生态发展取得的一系列令人振奋的新功能,同时继续围绕该计划继续推动健康的生态系统发展。

「Intel Pathfinder助力RISC-V生态繁荣发展」https://www.design-reuse.com/news/53136/intel-pathfinder-for-risc-v-ecosystem.html——Design & Reuse

近日,Andes发布了AndesCore的新成员™ 45系列,具有Linux多核和1024位矢量处理功能的AX45MPV。AX45MPV面向具有大量数据的应用,如数据中心AI推理和训练、ADAS、AR/VR、计算机视觉、密码学和多媒体。

「Andes发布多核RISC-V矢量处理器:AX45MPV」https://www.design-reuse.com/news/53155/andes-risc-v-multicore-1024-bit-vector-processor.html——Design & Reuse

纽瑞芯科技在本次论坛上正式发布了高性能UWB定位通信系统芯片NRT82800系列。该芯片面向智能手机和AR/MR,具有以手机为基点测量和监控其他UWB设备的空间位置的定位测距,以及感知手机周边的人、动物和移动物体、高速低延时数传、定位导航、移动支付、数字钥匙的雷达感知功能。

该系列芯片内置芯来科技RISC-V N300系列处理器内核。「纽瑞芯发布高性能UWB定位通信系统芯片,内置芯来RISC-V内核」

图片来源:纽瑞芯科技

——芯来科技

OmniXtend是一种开源架构,用于将处理器(或服务器)群集布到网络上的远程存储和内存系统。基于这种架构,RISC-V CPU等处理器可以基于网络去远程执存储系统上的程序。处理器将远程存储的程序或数据存储在本地存储器中。同时,它仍然可以保持整个内存层次结构中的数据一致性,保持整个网络中的信息一致,因此如果一条信息被更新(本地或远程),处理系统不会使用过时的数据,从而保持正确性。

「LeWiz开源了RISC-V的OmniXtend集群技术」

https://www.design-reuse.com/news/53188/lewiz-risc-v-with-omnixtend-clustering-open-source.html

Imperas宣称,日本电装旗下开发功能安全和下一代嵌入式系统处理器IP的集团公司NSITEXE,Inc.已经认证了NSITEXE-Akaria处理器的Imperas RISC-V参考模型。仿真模型是SoC架构探索和早期软件开发的重要起点。由于对设计决策和进度的影响,参考模型的质量和可靠性是开发人员实现总体上市时间目标的重要组成部分。

「Imperas为Akaria处理器NS72A、NS72VA和NS31A提供的RISC-V参考模型获得了NSITEXE认证」

https://www.design-reuse.com/news/53193/nsitexe-imperas-risc-v-reference-models.html

12月12日,芯昇科技有限公司携两款RISC-V内核物联网通信芯片在“2022中国移动全球合作伙伴大会——物联网分论坛”上精彩亮相。

CM6620是中移芯昇科技首款基于RISC-V内核架构的低功耗NB-IoT物联网通信芯片,采用芯来科技300系列RISC-V CPU IP内核,最低功耗0.9μA,具有丰富的外设资源,结合多电源域设计和优化的时钟门控策略,有效降低了系统功耗。同场发布的CM8610是业内第一颗基于RISC-V内核架构的LTE芯片,采用芯来科技600系列RISC-V CPU IP,采用22nm工艺,具备优异的射频性能、极简的BOM,并且支持Open CPU,可以广泛应用在中低速物联网应用场景。「芯来助力中移芯昇发布两款RISC-V内核通信芯片」

图片来源:芯昇科技

12月13日,据台媒TechNews报道,Arm策略与行销执行副总裁Drew Henry 在中国台湾的媒体分享会上表示,未来会在符合国际最新规范的基础上,依照客户需求,提供Arm架构解决方案,不会改变现有商业模式。谈到蓬勃发展的RISC-V产业时,Henry表示Arm正向看待这种良性竞争,相互竞争也让产业更清楚知道什么事情是重要的。

「Arm:不会改变现有商业模式,RISC-V带来良性竞争」https://laoyaoba.com/n/842005

近日,openEuler RISC-V SIG推出了一款基于openEuler的发行版——Eulaceura。

这是首个基于openEuler开发的RISC-V架构的发行版,给RISC-V的开发者开箱即用的RISC-V系统环境,方便开发者进行各种创新项目的开发与验证。「首个基于openEuler的RISC-V架构发行版Eulaceura发布」https://baijiahao.baidu.com/s?id=1751653299302059010&wfr=spider&for=pc——IT之家

Microchip在2022年RISC-V峰会上推出了一款基于RISC-V的FPGA,其能效是同类中端FPGA的两倍,并具有一流的设计、操作系统和解决方案生态系统。并展示其PolarFire 2 FPGA硅平台和基于RISC-V的处理器子系统和软件套件路线图。并讨论一种基于RISC-V的高性能空间飞行计算(HPSC)处理器,该处理器正为NASA和航空航天及国防工业开发。

「Microchip在RISC-V峰会上展示了基于RISC-V的FPGA和空间计算解决方案」https://www.design-reuse.com/news/53168/microchip-risc-v-fpga-space-compute.html——Design & Reuse

XMOS公布了其兼容RISC-V架构的第四代xcore平台。该平台提供了在软件中定义整个系统的灵活性,使RISC-V程序员能够快速实现智能物联网的最差异化和最经济的解决方案。

「XMOS宣布其软件定义SoC平台已兼容RISC-V」https://www.design-reuse.com/news/53189/xmos-software-defined-soc-platform-risc-v-compatible.html——Design & Reuse

近日,第二届滴水湖中国RISC-V产业论坛(简称“滴水湖论坛”)在上海顺利举办。来自北京嘉楠捷思信息技术有限公司、上海赛昉科技有限公司、酷芯微电子、珠海昇生微电子有限责任公司、时擎智能科技(上海)有限公司、武汉二进制半导体有限公司、泰凌微电子(上海)股份有限公司、芯昇科技有限公司、深圳市纽瑞芯科技有限公司、无锡沐创集成电路设计有限公司,以及北京中科昊芯科技有限公司的嘉宾进行了宣讲,共发布了11款本土RISC-V芯片新品,面向边缘计算、PC、汽车、无线通信、能源管理、安全等广泛应用。

其中,武汉二进制半导体有限公司、芯昇科技有限公司、深圳市纽瑞芯科技有限公司、无锡沐创集成电路设计有限公司此次发布的新品中均有芯来 RISC-V CPU IP的身影。——芯来科技

报告简介:首先总结几年来Linux发行版在RISC-V上的快速发展,通过重点剖析Fedora 从bootstrap到现在不断滚动更新的开发过程及当前成果,得以说明发行版对于软件生态的影响和重要性。然后,对当今各种主流的Linux发行版对于RISC-V的支持情况做简要的介绍,并对系统的重要组成部分做了现状介绍,例如Firmware、bootloader、Kernel等。最后通过介绍当前被主流Linux发行版支持的一些RISC-V开源硬件及开发板,展望未来几年在当前时代大背景下,在国家大力支持下,RISC-V从IOT到高性能领域的发展前景。

「开源芯片系列讲座第07期:基于RISC-V的Linux发行版及软件生态」——厦门市开源芯片产业促进会

随着各行业加速向RISC-V转变,开放标准指令集架构 (ISA) 正在引领新一波创新与协作。为了推动这一趋势,高度可扩展RISC处理器IP的领先开发商MIPS宣布推出eVocore P8700,是一款能够提供乱序 (OOO) 处理和一致的多线程、多核、多集群可扩展性的RISC-V IP内核。

「MIPS推出首款RISC-V IP内核:支持乱序处理、多线程、多核、多集群」——半导体芯闻

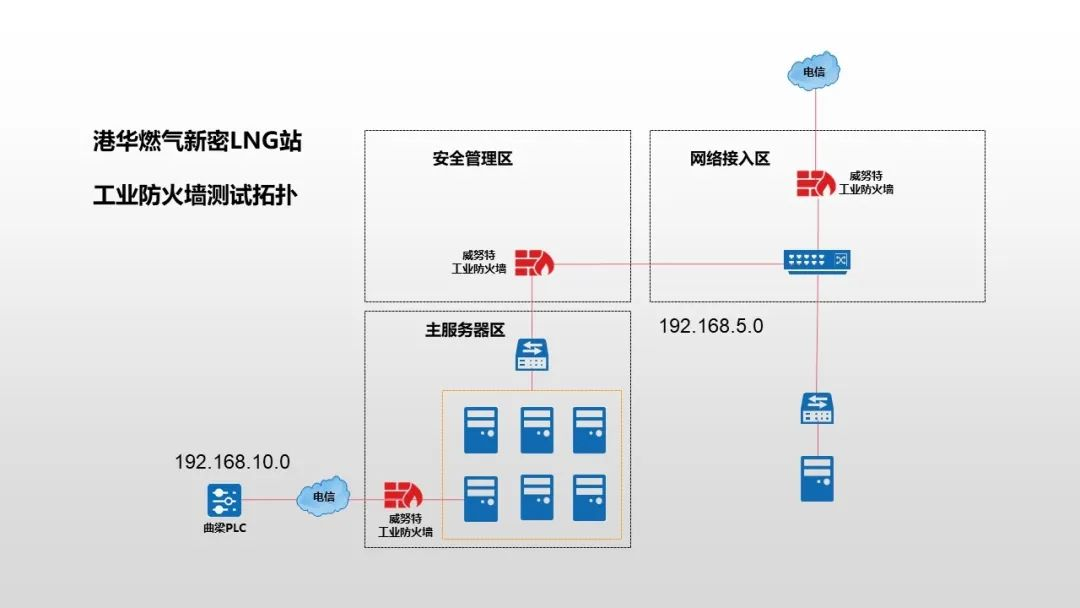

近日,首款基于RISC-V芯片的工业防火墙在能源行业获得阶段性新突破。产品基于赛昉科技提供的自研RISC-V SoC芯片,港华智慧能源的平台规范、能源行业的运营经验及资源,并搭载威努特自主研发的IICS-OS系统套件,可实现燃气运营场景下的全流程安全可控。

「阶段性突破!首款基于RISC-V芯片的工业防火墙完成实测!」——StarFive

沉芯基于RISC-V,将串行 MCU或者CPU与并行处理的自适应动态可重构架构相结合,实现串并行自由切换。

图片来源:Robei

——Robei

https://www.eetimes.com/examining-the-top-five-fallacies-about-risc-v/

https://baijiahao.baidu.com/s?id=1751134316309908949&wfr=spider&for=pc

https://baijiahao.baidu.com/s?id=1751251493755213078&wfr=spider&for=pc

香山双周报(第21期·2022-12-05)

https://mp.weixin.qq.com/s/-heIBMDiCGfblufySrfOvQ

PLCT开源进展(第40期·2022-12-01)

https://zhuanlan.zhihu.com/p/588704942

OpenArkCompiler Weekly(第142期·2022-12-11)

https://zhuanlan.zhihu.com/p/591020149

OSTD Weekly (第179期·2022-12-07)https://mp.weixin.qq.com/s/9UhxmbcTBd9faa52R_u2dQ

RISC-V Linux内核及周边技术动态(第24期·2022-12-11)https://mp.weixin.qq.com/s/wZ-TNwLhmobXmDrgdT5Tcg

更多实验例程

www.rvmcu.com