报名编号:CICC2469

团队名称:AM

学校名称:广东工业大学

队伍成员:林贤、刘合明、谢泽铭

指导老师:郑欣、高怀恩

环境:Ubuntu20.04、Iverilog12.0、gtkwave3.3.103

内容:Iverilog仿真e203_hbirdv2跑RISC-V指令测试用例

要点:

下载安装最新的Iverilog,sudo

apt-get install的版本太旧会出现各种问题

下载地址:https://github.com/steveicarus/iverilog

右边的Releases有最新的版本,最新是12.0,最稳定是11.0,搞12.0的。

安装教程:https://iverilog.fandom.com/wiki/Installation_Guide#Installation_From_Source

跟大部分的工具安装一模一样,也可以按照Iverilog压缩包里面的README.txt文件来,然后sh autoconf.sh生成configure文件,--prefix选择自己想要的安装路径,记得把路径加到环境变量文件里!

安装过程中,如果出现readline相关的报错就sudo apt install libreadline-dev,如果出现termcap相关的报错,则安装termcap库参考:https://blog.csdn.net/qq_45596493/article/details/103848179

下载安装成功后,在终端输入iverilog -v的命令,输出:

则安装成功。

安装gtkwave:直接sudo

apt-get install gtkwave

安装成功后,在终端输入gtkwave --version的命令,输出:

则安装成功。

接下来参考e203/e203_hbirdv2/vsim目录下的README.md文件进行操作即可跑测试用例:

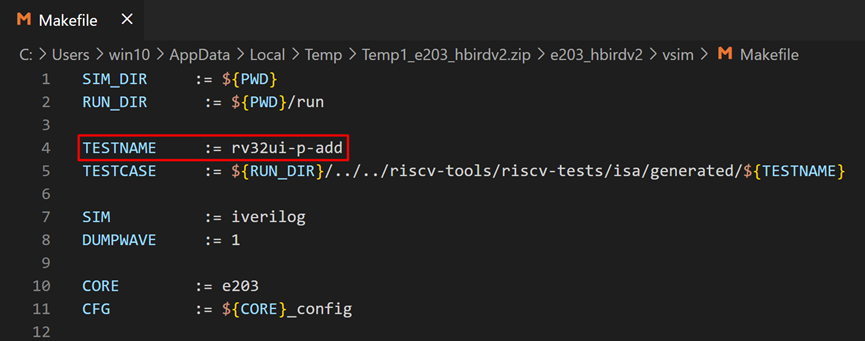

上图README.md里红框这一句是自己改的,因为e203/e203_hbirdv2/vsim目录下的Makefile文件里面的TESTNAME是写死的,每次只能跑rv32ui-p-add,没改之前是:

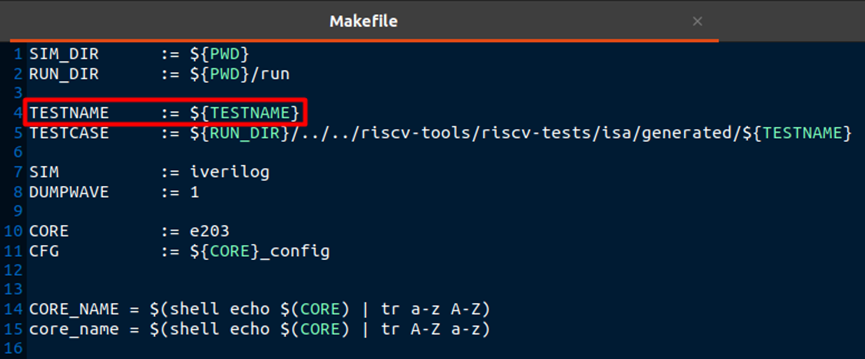

改了之后,我就可以通过指定文件名字来跑我想跑的测试用例啦,可喜可贺可喜可贺:

最后,

make clean

make install

make compile SIM=iverilog

make run_test SIM=iverilog TESTNAME=rv32ui-p-add

输出:

则仿真成功。

参考文章:

https://blog.csdn.net/appleyao/article/details/103250896

https://blog.csdn.net/whik1194/article/details/103377834

https://www.jianshu.com/p/df52e2350c77

https://blog.csdn.net/appleyao/article/details/103252053

https://blog.csdn.net/qq_45596493/article/details/103848179

https://blog.csdn.net/m0_52394388/article/details/120555896

https://blog.csdn.net/qq_39816087/article/details/101844899