团队编号:CICC1413

团队名称:“芯”之所向

首先声明本文所画图片仅在本人分析add指令过程时所画下,便于日后分析输入输出信号如何流通、传出,因此部分不相关内容未在图中画出。本文中若存在不正确的地方欢迎指正。

首先先指出图中不包含的三个输入信号:

i_prdt_taken表示在预测执行过程中,处理器是否预测、跳转或分支会被执行,如果预测到会被执行,则该信号为1,否则为0。、

i_misalgn表示IFetch请求的地址是否对齐。

i_buserr表示IFetch请求的地址是否在系统总线上存在错误。

这三个信号在图中并未画出,其输入之间连着输出,在该模块中只起到传导作用。

剩余在图中所画的信号命名都相对较为直白,在此仅解释下列2个信号:

dec_info信号根据xxx_op信号将其对应的模块信息xxx_info_bus对其进行赋值,例如当执行add指令时,其alu_op为1,其余xxx_op为0,此时dec_info = alu_info_bus。

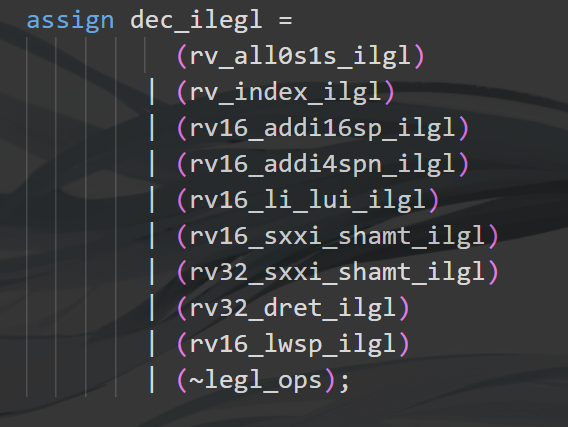

dec_ilegl信号汇集了各种在译码阶段出现的不合法的(illegal),例如指令全0或全1异常、寄存器索引异常等,这些异常信号之间为或的关系,只要出现一个异常则信号输出高。