报名编号:CICC1764

团队名称:两年半IC练习生

我们在做参赛课题的过程中发现,上FPGA开发板跑系统时,有时需要添加vivado的ip核。但是vivado仿真比较慢,vcs也不能直接对添加了vivado ip核的soc系统进行仿真。在这种情况下我们可能就需要用到vcs核vivado联合仿真。

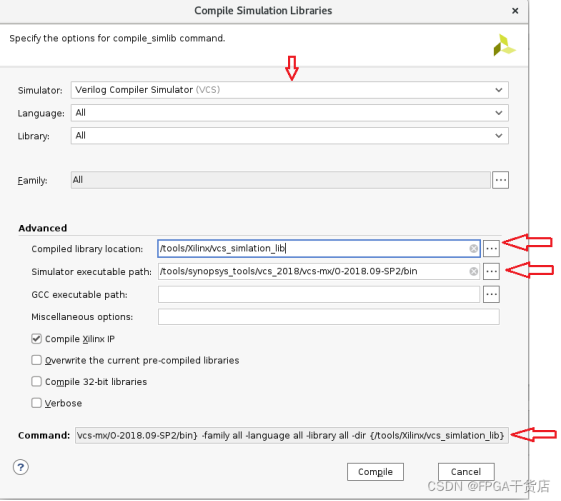

1.Vivdao仿真库编译

打开vivado软件,点击Tools–>Compile Simulation Libraries;

(1)Simulator选择:VCS;

(2)Compile library location:设置你需要编译仿真库的位置(该位置你自己定义);

(3)Simulator executable path:设置仿真执行文件的路径,即安装VCS目录下的执行指令位置;

(4)Command:当你选择完成后,会在此Command的窗口上显示对应的tcl指令,需要copy出来使用tcl指令界面编译;

原因在于:正常的话我们直接点击Compile进行编译就可以了,但是直接编译后会产生systemc的编译错误;是由于vivado2021.2版本与vcs2018的版本不匹配问题造成。在ug900文档中明确描述vivado2021.2版本对应VCS的版本是2020.12,由于license问题所以选择vcs2018的版本;虽然目前与官方的版本不匹配,但是不影响正常使用;

使用tcl界面查询compile_simlib指令使用;将上述的Command编译指令copy下来后,再添加-no_systemc_compile选项进行编译,就开始对Vivado的仿真库进行编译。

注意:在使用vivado2021.02编译VCS仿真库时一定要加-no_systemc_compile选项进行编译,否则编译会出现systemc的错误,主要也是版本不匹配问题;

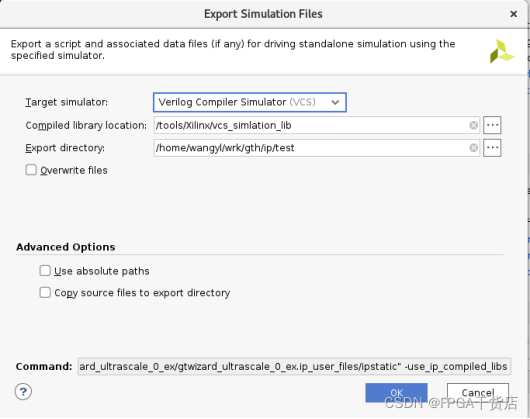

2.在打开的工程中选择File–>Export Simulation

将脚本导出来后,发现工程目录下多了一个VCS文件夹,在VCS目录下有一个*.sh脚本文件,仿真直接执行该脚本就可以。

在vcs文件夹下输入仿真命令如下:

./tb_top.sh

verdi -f filelist.f -ssf tb_top.fsdb

即可实现用vcs和verdi对rtl代码进行仿真。

参考网址:https://blog.csdn.net/houzi6320/article/details/126768482