团队编号:CICC1230

团队名称:少吃米饭多吃肉

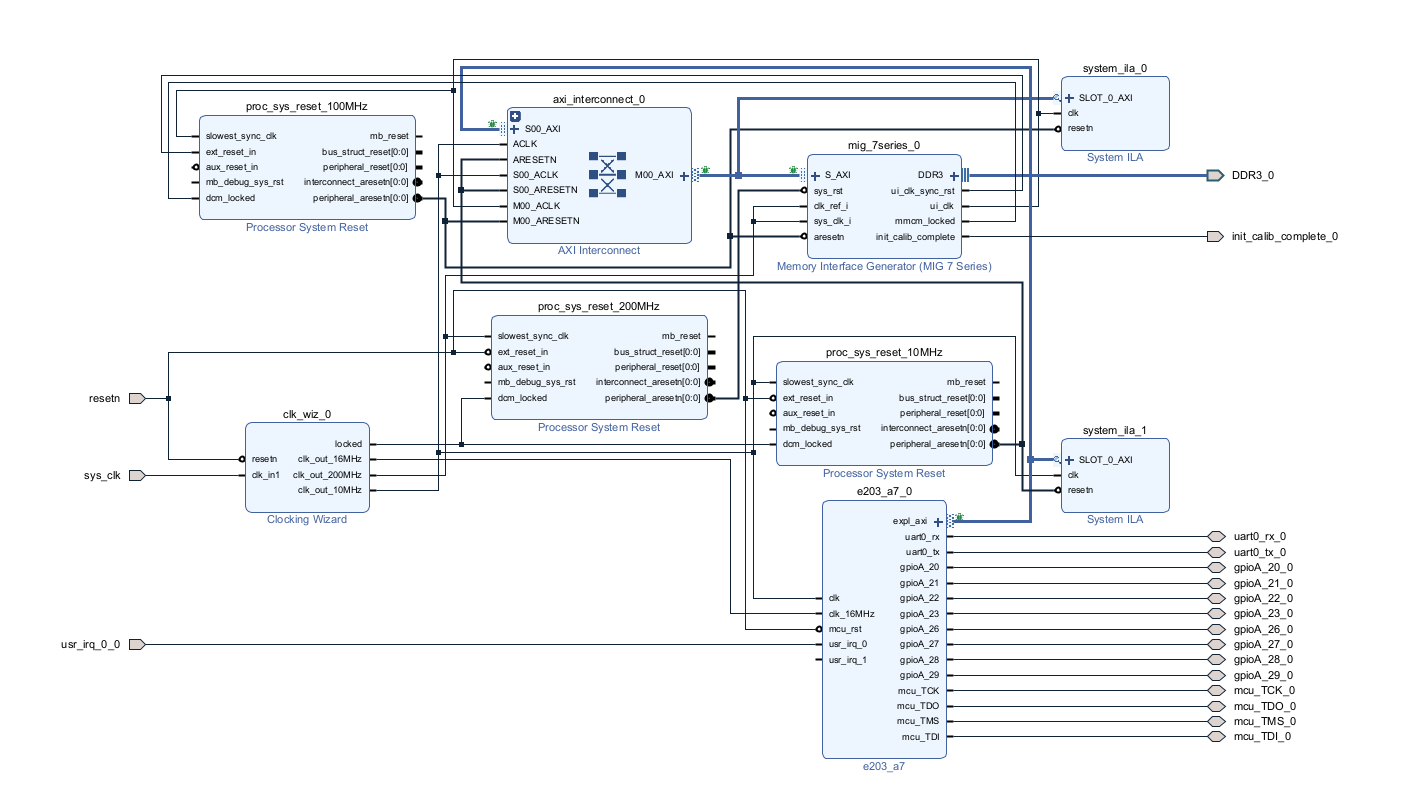

蜂鸟e203中的存储功能极为有限,对一些大规模存储运算而言,其难以满足要求。故我们可以将板子中的ddr存储资源利用起来,其可通过内核中的icb转axi总线与vivado中的mig ip模块进行连接,从而达到一个控制ddr存储的效果。如有错误,欢迎评论指出。

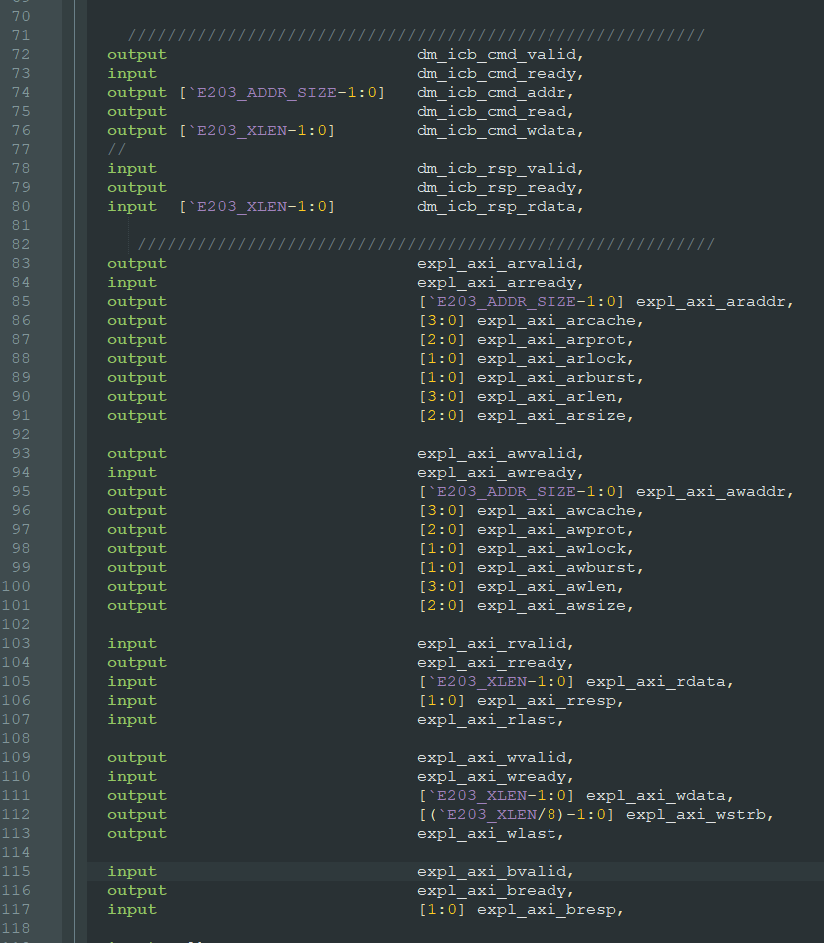

蜂鸟e203内部使用的是icb总线,这种总线协议与AXI类似,都采用了握手信号进行传输;而在e203的内部也给我们提供了一份icb转换为axi的示例,其位于/subsys/ e203_subsys_mems.v文件中,我们可将其层层引出直至顶层当作一个AXI-MASTER来使用。引出的顺序为e203_subsys_mem -> e203_subsys_main -> 203_subsys_top -> e203_soc_top。这里 选择e203_subsys_mems.v文件中的O5作为从设备的基地址,AXI的输入输出端口如下图所示.(将icb转为axi端口时,需将里面的sirv_expl_axi_slv模块注释掉,否则会报出端口被重复定义的错误)

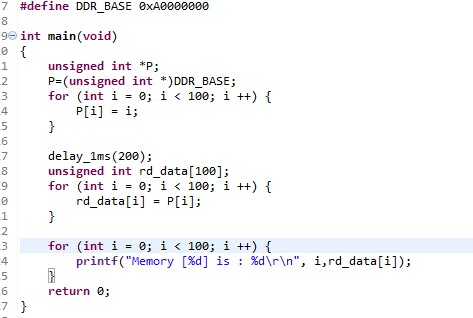

可通过e203内核往ddr里面写入数据,再将ddr的数据取出来验证其是否正确。注:ddr的基地址我们在步骤一中设为A0000000,软件代码定义的寄存器基地址须在其范围里面,代码如下图所示