团队编号:CICC1649

团队名称:巴巴托斯

团队成员:杨浩溢,赖小均,董川江

引言

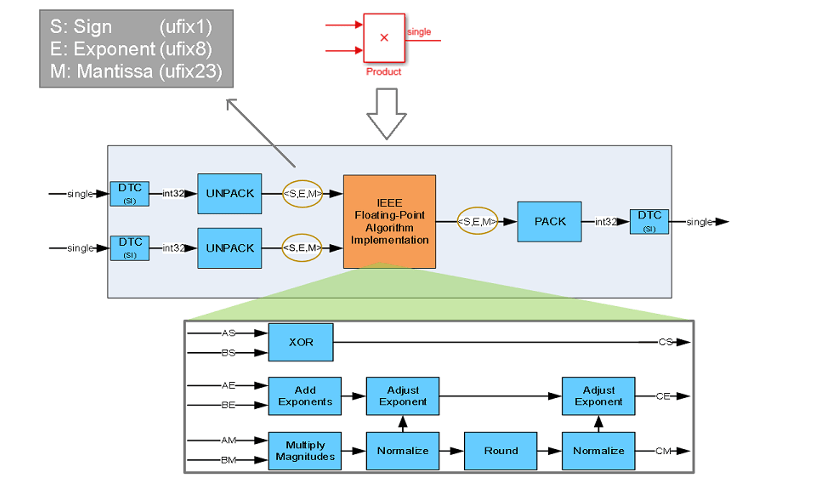

想要实现浮点运算功能,如果自己写Verilog代码,需要花费较多的时间和精力。好在Simulink HDL Coder工具箱提供了自动代码生成技术。下图展示了HDL Coder如何生成浮点运算单元。

Unpack和Pack模块块将浮点类型转换为符号、指数和尾数。图中S、E、M分别代表符号、指数、尾数。这是基于IEEE-754浮点运算标准。浮点算法实现块在S、E和m上执行计算。通过这种转换,生成的HDL代码与目标无关。可以在任何通用FPGA或ASIC上部署该设计。

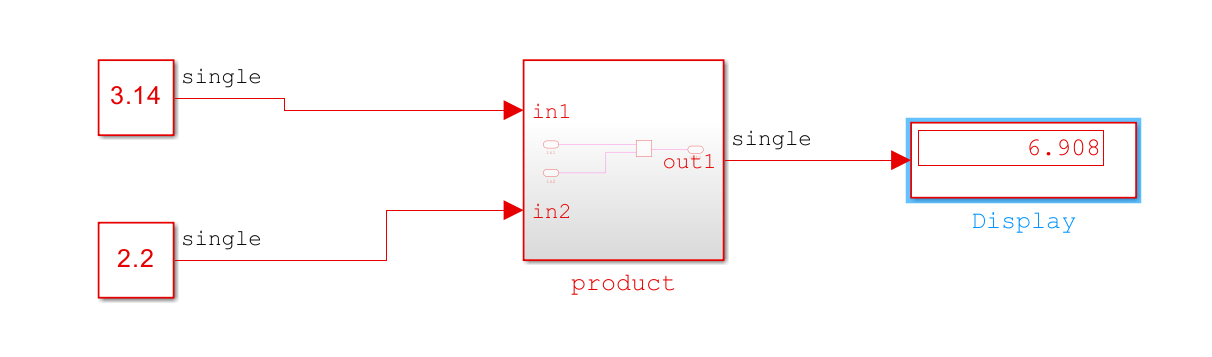

下面介绍如何在Simulink中创建单精度浮点乘法

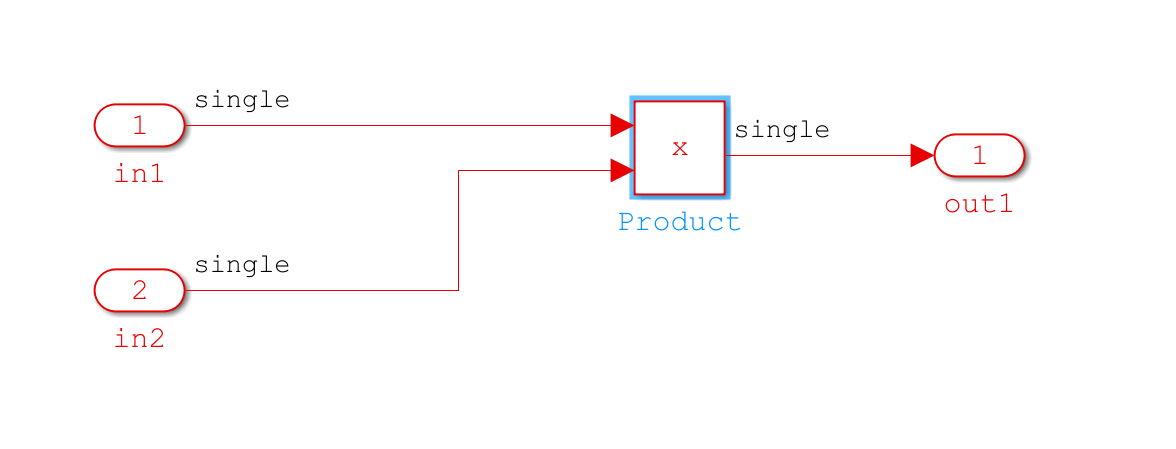

直接使用乘法模块即可,并将输入口改为单精度浮点

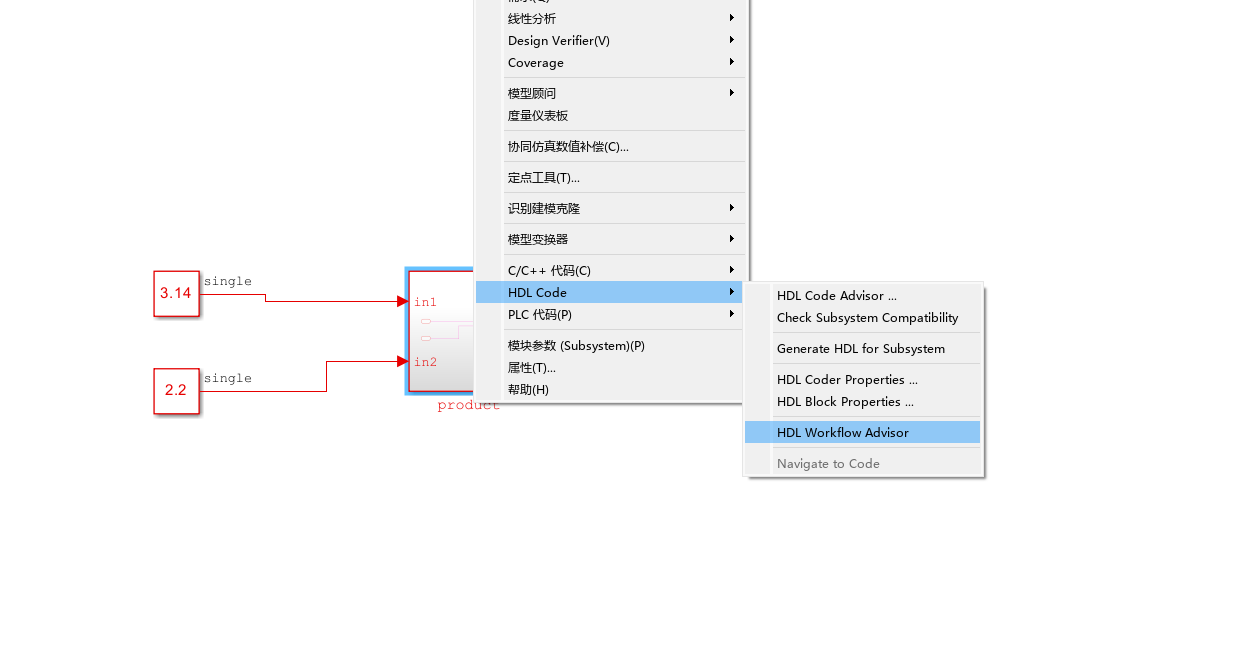

使用Ctrl + g 封装在模块中,方便使用HDL Workflow Advisor

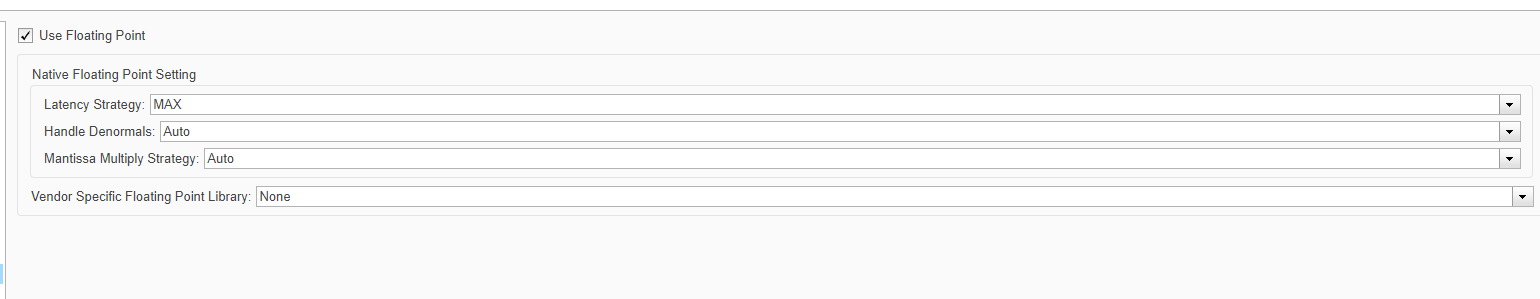

Ctrl + E 并勾选使用浮点

右击模块并启动HDL Workflow Advisor

按照步骤即可生成HDL代码

查看生成的代码

下图是顶层模块

由于浮点算法模块太长,这里就不贴了。

参考链接https://ww2.mathworks.cn/help/hdlcoder/ug/generate-target-independent-hdl-code-with-native-floating-point-libraries.html

想要了解更多关于自动代码生成技术,可以参考Mathworks官方文档的HDL Coder工具箱。