将subsys_mem.v 文件内AXI总线信号引出后,将项目完成综合与implement,此时可以创建新的IP

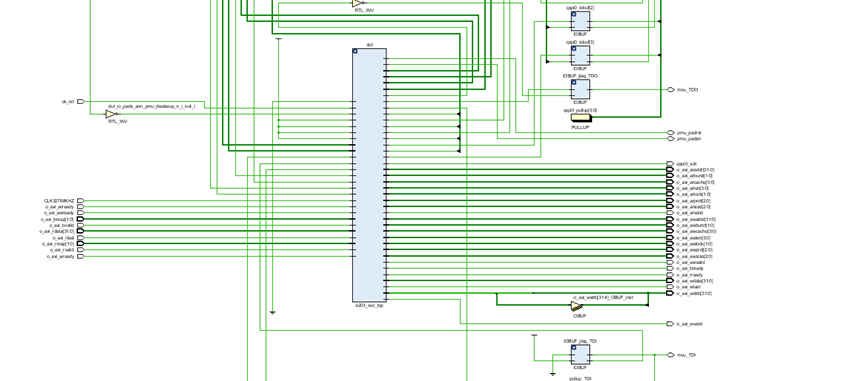

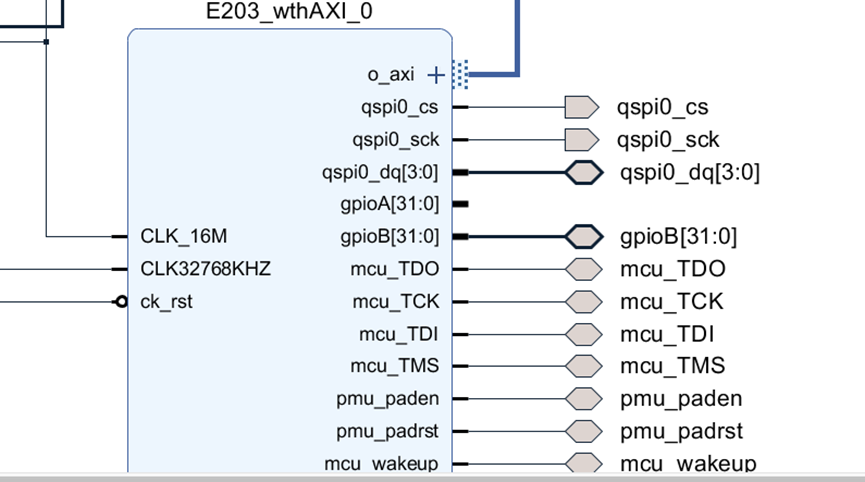

此时要注意的是,e203引出的AXI总线信号应该和mem.v的子模块icb2axi.v内AXI相关信号的方向一致,传出后,命名规则一致的信号会汇总为同一条总线,即图中的o_axi总线

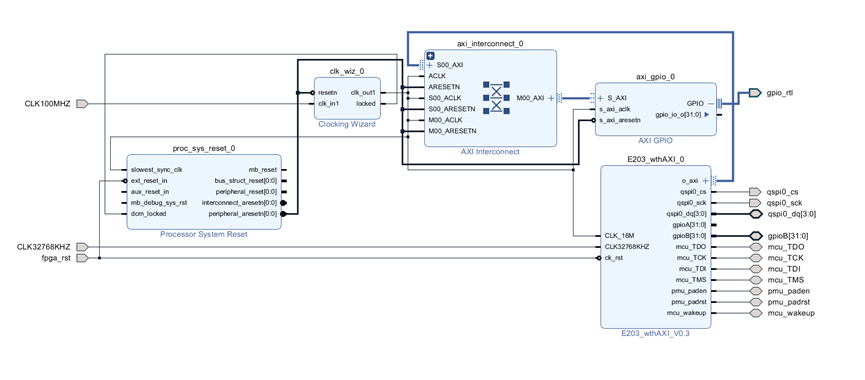

到此,e203就加上了AXI总线,但是不能够顺利综合,原因是E203IP 在blockdesign中与其它IP组合成系统后,其时钟信号与复位信号应当保持一致,即e203内部的ck_rst信号与CLK_16M信号都应该引出到外界,再在blockdesign界面中加入clk_wiz模块IP与复位IP,在blockdesign中生成16MHz时钟信号接到e203,而e203内部不做任何IP调用。

这时,系统就能validate正常,随后的XDC文件按照master.xdc并根据wrapper.v文件中的IO定义来修改具体约束

在做的时候遇到过一些错误,相应的解决方案为:

1、将引出AXI总线后的E203包装为IP后,在blockdesign阶段显示缺少FREQ_HZ参数,这一参数可以在ip creator工具界面中的IO选项中选中AXI总线,点击edit找到parameter一栏中手动添加,或者在blockdesign阶段中补完,不是大问题

2、在包装IP时,需要注意的是AXI总线的时钟问题:必须在IO选项中选择AXI总线并右键点击clock选项,选定到16MHz时钟对应的时钟信号

3、在包装E203时,原本的IP,MCLK与ASYN_RST最好在ip_creator工具中选择保存.xci文件的选项