队伍编号:CICC3280 团队名称:芯新星队

本文主要讲解RISC-V指令集手册中F指令部分

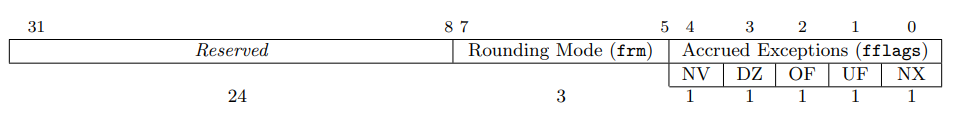

RISC-V标准中采用了符合IEEE 754-2008算术标准的单精度浮点计算指令,对于浮点运算来说,RV32F指令扩展中增加了32个32位的浮点寄存器,f0-f31,并且还有一个单独的浮点控制状态寄存器fcsr。绝大多数浮点指令都直接对浮点寄存器中的值进行操作。fcsr寄存器的格式如图十六所示:

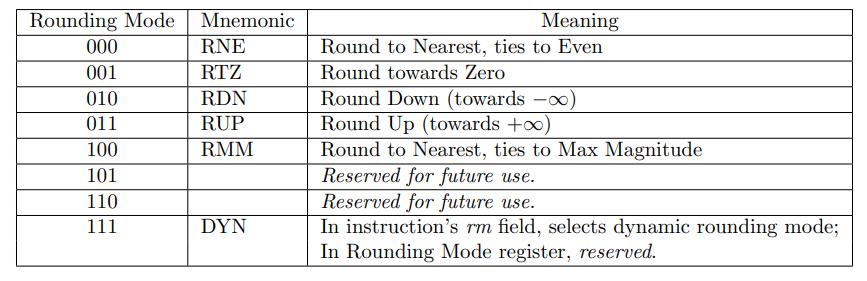

fcsr寄存器不仅可以被完整地访问,也可以按域单独访问,frrm/fsrm伪指令用于单独访问fcsr的frm域,frflags/fsflags伪指令可以单独访问fcsr的fflags域。fcsr中31-8位进行保留,以便后续扩展,7-5位为舍入模式的设定。舍入模式可以分为静态舍入和动态舍入,静态舍入即按照浮点指令内固定的模式去执行,动态舍入可以通过frm域的值动态选择,此时指令编码中的rm域为111,无效的舍入会引起非法指令异常。RISC-V规定的舍入模式如图十七所示:

舍入模式分为

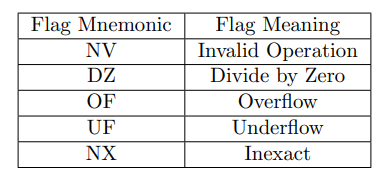

fcsr的4-0位表示异常标志,每一位对应一个异常情况,如图十八所示:

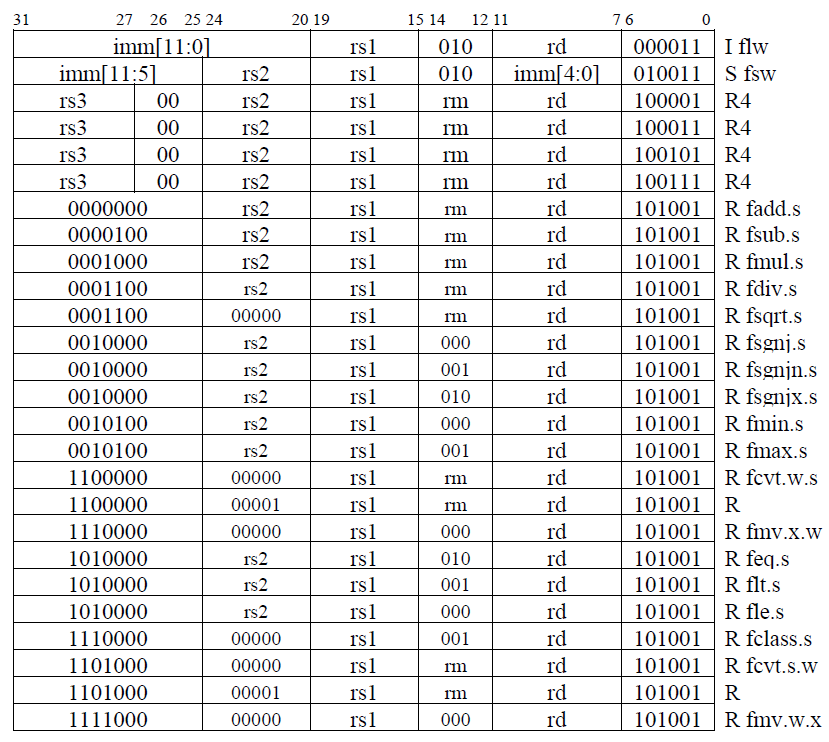

F指令详细的指令信息可参考RISC-V官方手册或《手把手教你设计CPU》,在此仅将指令信息列表给出不做过多赘述。(F指令列表如图十九所示):

注:\infty在MathJex中表示无穷大