喜欢0次

学校:安徽工业大学

团队名称:能用就行队

团队编号; CICC1849

团队成员:高志强,叶颖,汪志泉

指导老师:王玲玲

由于目前对于蜂鸟e203来使用vivado综合时太费时间,一般性能的电脑需要运行十分钟以上很耽误开发效率,所以我们提供Vivado增量编译的方式加快综合速度和提高效率。

Vivado增量编译的方式加快综合速度

如何打开启用增益编译操作?

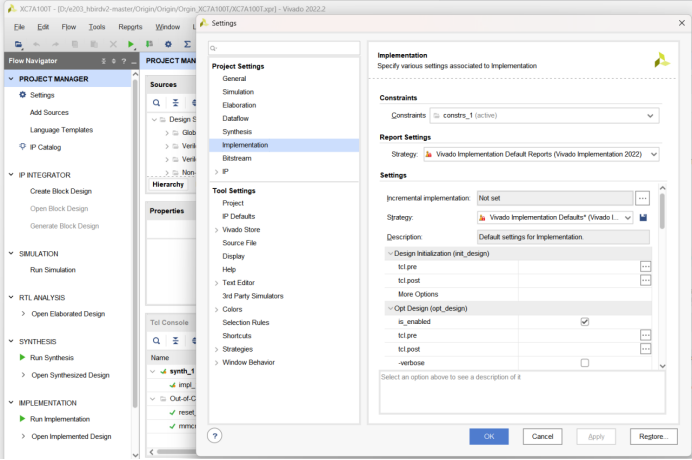

(1)打开“Settings”菜单并选择“Project Settings”下的“implementation”。

(2)在options窗口下,选择“Incremental compile”,点击选择文件窗口,如下图所

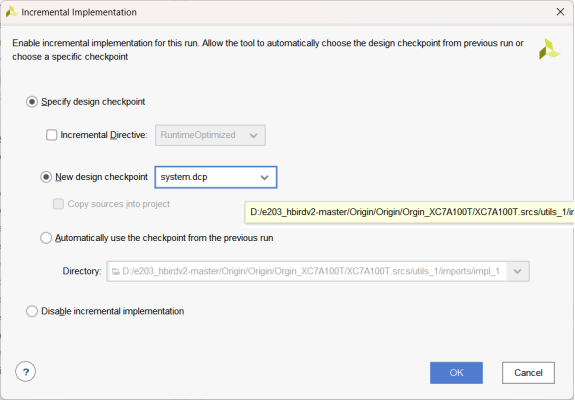

(3)弹出文件选择框,点击“打开当前目录”,再打开“.runs”->“impl”,选择“*dcp

到此我们已经设置好了vivado增量编译的方式来加快综合速度