喜欢0次

队伍介绍:

报名编号:CICC1829

团队名称: 你说的对对队

这是我们队伍的第5篇帖子

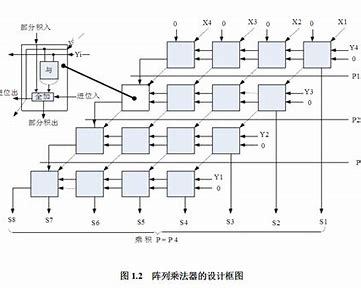

蜂鸟E203原有的软核处理器是利用booth 4 算法从低位到高位迭代生成一个一个部分积,然后与之前的部分和送至数据通路加和生成下一个部分和。依次迭代17个时钟周期可以得到最终的乘法器结果,这种方法的优点是面积很小,消耗的资源也很少,但缺点就是计算速度太慢。

我们设计了 booth 4阵列,对输入模块MDV的源操作数rs1 和 rs2 直接进入 booth 4 阵列,产生17个部分积,然后在进入wallace加法树,并行产生 最终两个64bit操作数op1 、op2,进入数据通路,相加得到最终结果。