喜欢0次

如标题所示,我们分享关于蜂鸟SOC的SPI外设中,SPI的时钟相位和时钟极性

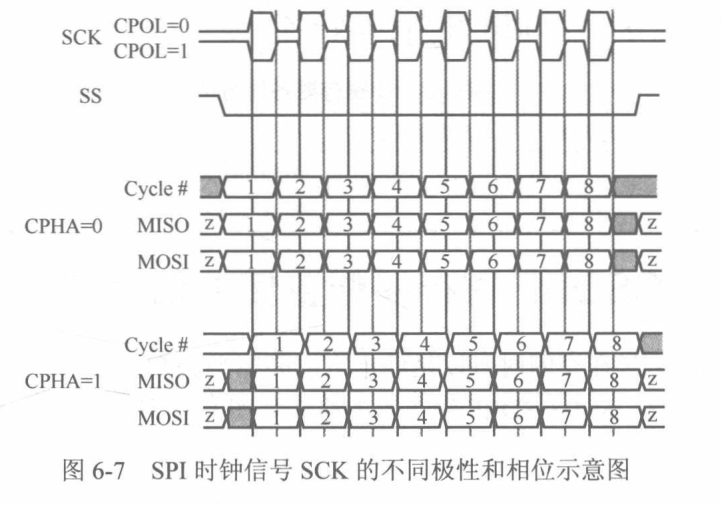

SPI的时钟相位和时钟极性相关概念如下图:

SOC的SPI0外设默认为 CPHA = 0, 但是我们的采样模块需要 CPHA = 1,所以我们修改SPI的RTL代码。

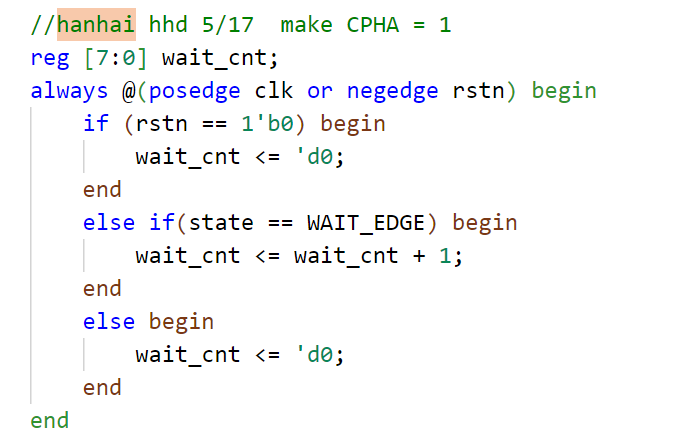

修改spi_master_controller.v:

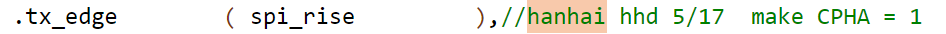

将边沿条件spi_master_tx/rx的边沿条件更改:

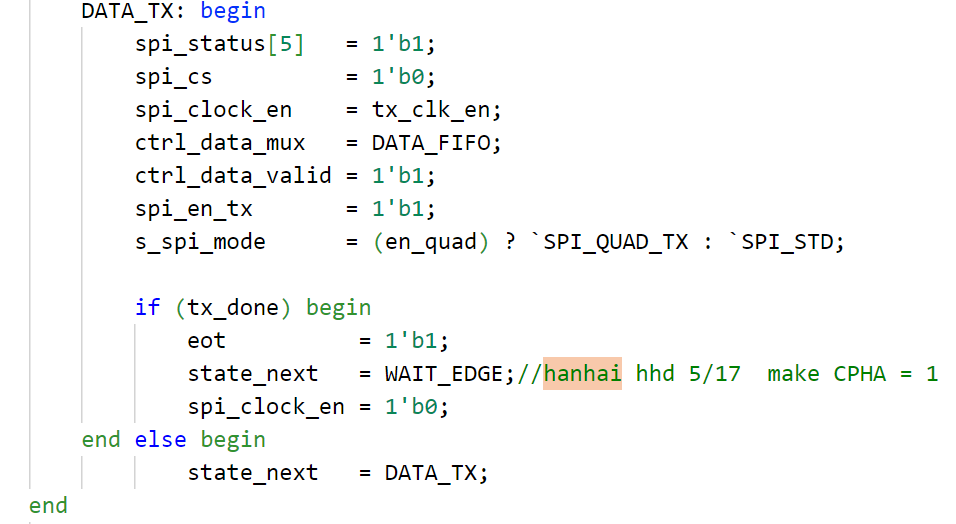

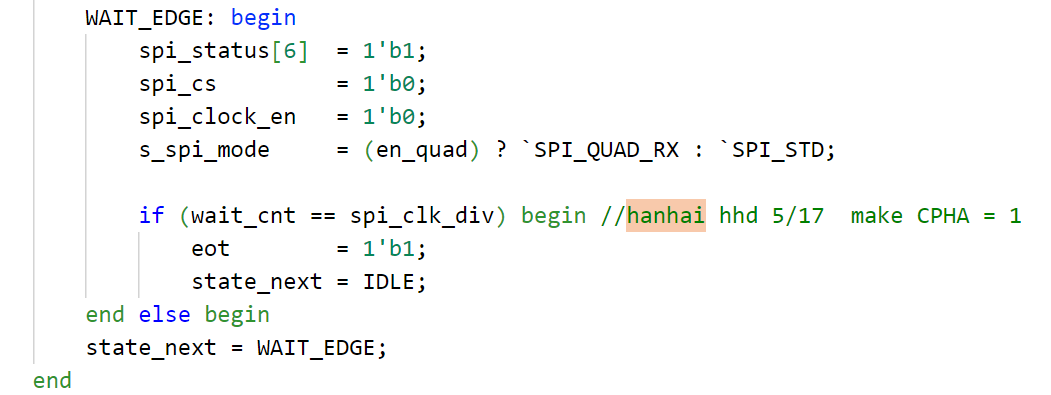

更改状态机,使结束时间多半拍:

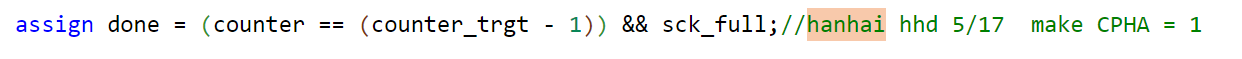

spi_master_rx/rx中的done信号等需要改变:

抛砖引玉,谢谢大家