队伍编号:CICC4901

队名:唯唯诺诺搞设计

文章《32位RISC-V处理器中乘法器的优化设计》(链接:https://kns.cnki.net/kcms2/article/abstract?v=3uoqIhG8C44YLTlOAiTRKibYlV5Vjs7iJTKGjg9uTdeTsOI_ra5_Xa7w7cyx8Qk2woSl8YjwVYwmyyV_3LWKKR6bkP9ZTQE-&uniplatform=NZKPT)

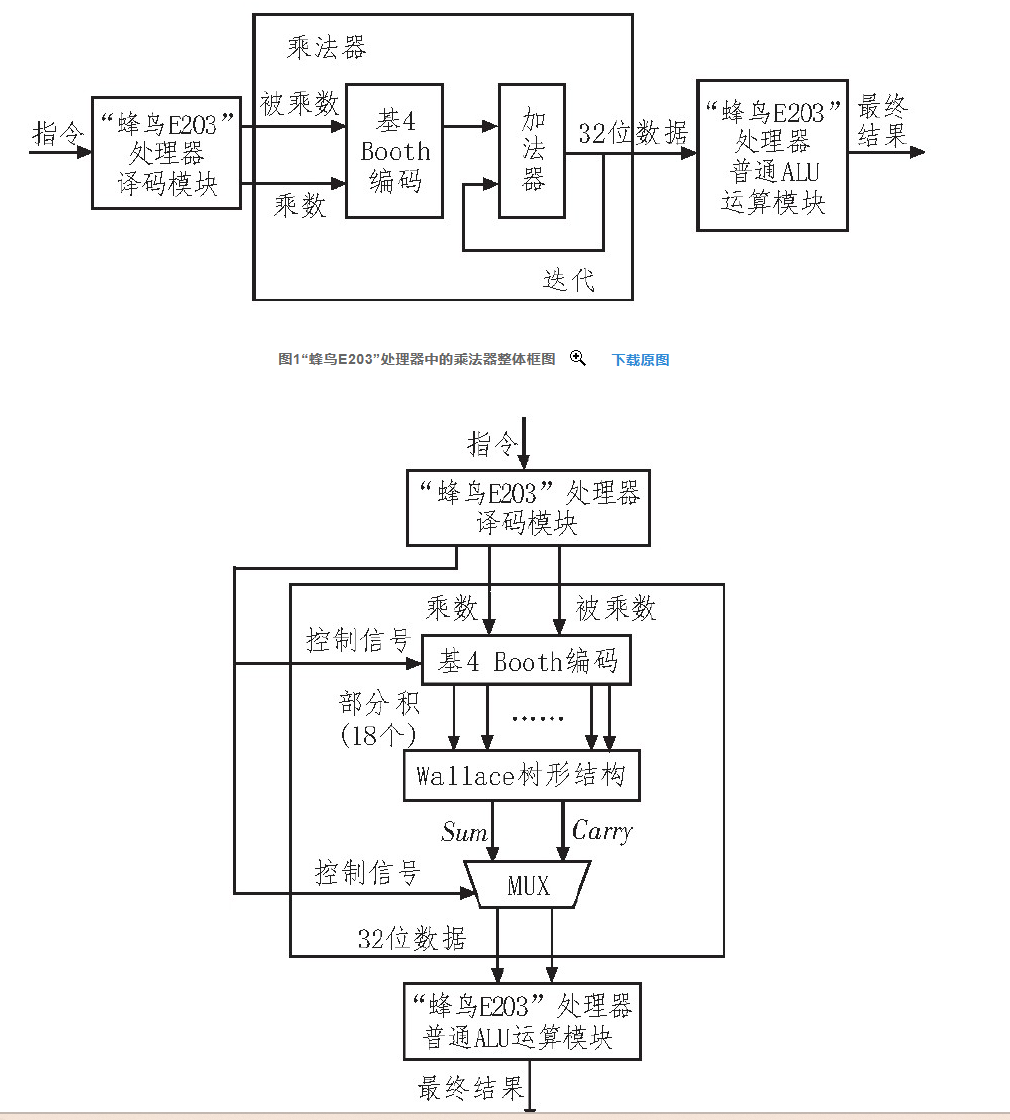

提出了一种基于E203处理器的乘法器优化设计方法,核心改进如下图:

改进后的乘法器:译码模块对乘法指令进行译码,基4 Booth编码接受控制信号后,对乘数进行符号扩展,并产生18个规整的部分积,经Wallace树形结构压缩,得到求和Sum与进位Carry两个部分积,MUX通过控制信号选取Sum或者Carry的高32位/低32位,传输到ALU模块进行运算,得到乘法结果。

其中Wallace树形结构的压缩器是该算法的核心,乘法器的延时主要由压缩器在对部分积结果进行压缩时的延时造成,文章对压缩器进行了优化和合理排列,提出了一种新型的5-2压缩器和新型的Wallace树形压缩结构(分别见原文2.1.1和2.1.2节)。

乘法器性能改善效果:

源码的乘法器周期数解读:在文件exu_alu_muldiv中,实现了17周期的乘法单元和33周期的除法单元,主要是与ALU_DPATH模块共享数据路径,将门数降到最低。