队伍CICC2259 队员:刘宇轩 周嘉琪 冷思远

RISC-V支持16位压缩格式,压缩格式立即数位数更少,能使用的寄存器也比较少,有些指令只能用常用8个整数寄存器(x8-x15)或者(f8-f15)。16 位指令只对汇编器和链接器可见,并且是否以短指令取代对应的宽指令由它们决定。

为了能在一系列的程序上得到良好的代码压缩效果, RISC-V 架构师精心挑选了 RVC扩展中的指令。同时,基于以下的三点观察,架构师们成功地将指令压缩到了 16 位。

1、对十个常用寄存器(a0-a5, s0-s1, sp 以及 ra访问的频率远超过其他寄存器。

2、许多指令的写入目标是它的源操作数之一。

3、立即数往往很小,而且有些指令比较喜欢某些特定的立即数。

因此,许多 RV32C 指令只能访问那些常用寄存器;几乎所有的立即数都被缩短了, load 和 store 操作只使用操作数整数倍尺寸的无符号数偏移量。

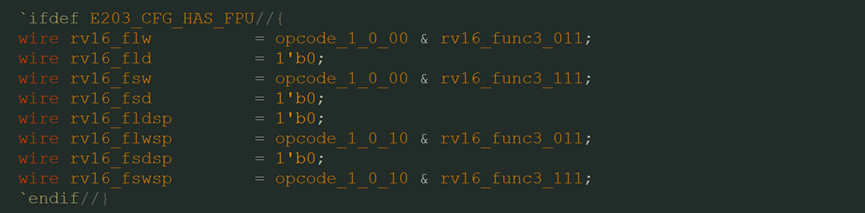

蜂鸟e203为我们预留了浮点相关的16位指令扩展接口,我们只需要添加相应的译码过程即可。在这里我们根据需要添加了rv16_flw,rv16_fsw,rv16_flwsp,rv16_fswsp。

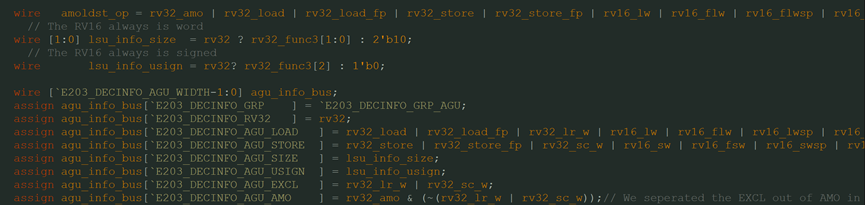

这四条指令皆为需要使用到AGU和LSU的长指令,我们必须将它们的译码结果添加到发送给AGU的总线当中。

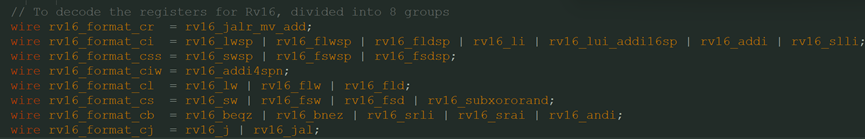

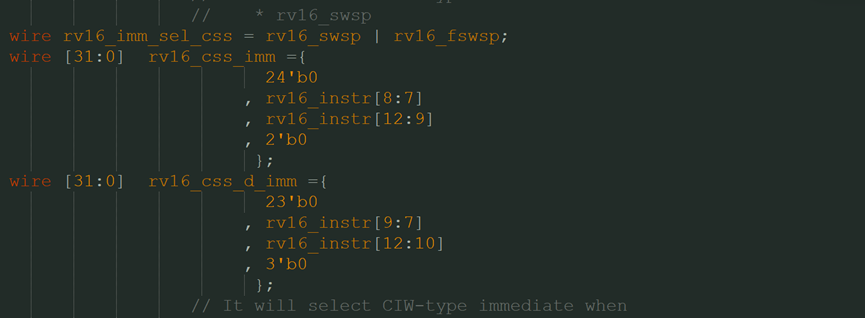

为了能够译码得到rv16的寄存器值,我们必须要把它们分为8组。因为不同组别的立即数译码过程也是不同的,分别对应了八套不同的立即数译码方案。所以,我们需要在相应的分组中添加我们刚刚添加的指令。

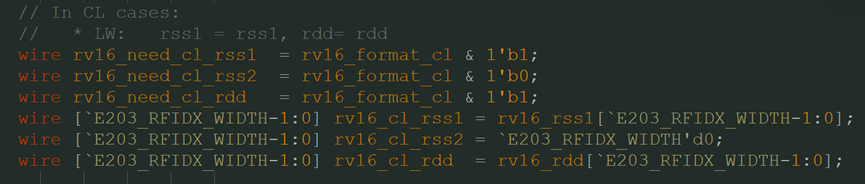

而它们需要哪些寄存器,以及需要寄存器参数的类型也要根据之前得到的分组情况来进行判别。此处举了分组CL的例子,判别结果是这一组CL指令都需要rs1和rs2,但不需要rd。