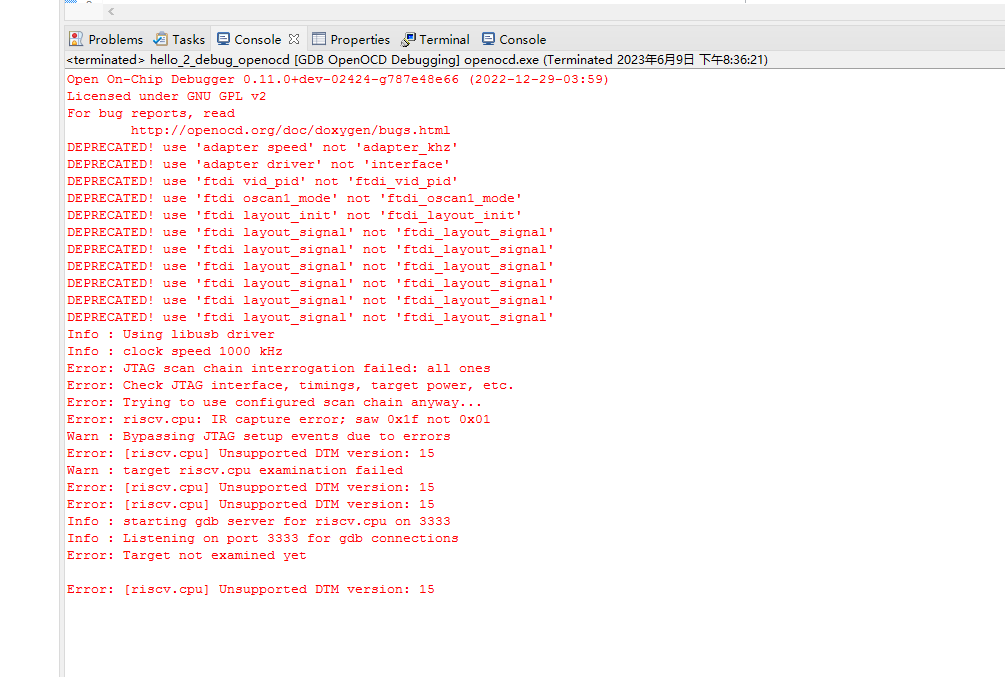

我将E203移植到ZYNQ ZU15EG上后,可以运行,但在向其加载程序时,始终报错,报错信息如下,

之前程序烧录成功过两三回,但后来却无法重复了,抓取jtag波形,也有显示,不知道问题出在哪里,

](/uploadfile/editor/0/5/5480.png)

使用的调试器是这款,连线TDI、TDO、TMS、TCK、GND、5V、3.3V七根

约束文件整体如下:

create_clock -period 20.000 -name sys_clk_pin -waveform {0.000 10.000} -add [get_ports CLK50MHZ]

set_property PACKAGE_PIN J17 [get_ports fpga_rstn]

set_property IOSTANDARD LVCMOS33 [get_ports fpga_rstn]

set_property -dict {PACKAGE_PIN F16 IOSTANDARD LVCMOS33} [get_ports mcu_TDI]

set_property -dict {PACKAGE_PIN J10 IOSTANDARD LVCMOS33} [get_ports mcu_TMS]

set_property -dict {PACKAGE_PIN J12 IOSTANDARD LVCMOS33} [get_ports mcu_TDO]

set_property -dict {PACKAGE_PIN J11 IOSTANDARD LVCMOS33} [get_ports mcu_TCK]

set_property KEEPER true [get_ports mcu_TMS]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets design_1_i/system_1/inst/dut_io_pads_jtag_TCK_i_ival]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets design_1_i/system_1/inst/IOBUF_jtag_TCK/O]

set_property -dict {PACKAGE_PIN G13 IOSTANDARD LVCMOS33} [get_ports uart0_tx]

set_property -dict {PACKAGE_PIN G11 IOSTANDARD LVCMOS33} [get_ports uart0_rx]

set_property -dict {PACKAGE_PIN A17 IOSTANDARD LVCMOS33} [get_ports gpioA_0]

set_property -dict {PACKAGE_PIN L19 IOSTANDARD LVCMOS33} [get_ports gpioA_1]

set_property -dict {PACKAGE_PIN K20 IOSTANDARD LVCMOS33} [get_ports gpioA_2]

set_property -dict {PACKAGE_PIN L20 IOSTANDARD LVCMOS33} [get_ports gpioA_3]

set_property -dict {PACKAGE_PIN L18 IOSTANDARD LVCMOS33} [get_ports gpioA_4]

set_property -dict {PACKAGE_PIN C16 IOSTANDARD LVCMOS33} [get_ports gpioA_5]

set_property -dict {PACKAGE_PIN A15 IOSTANDARD LVCMOS33} [get_ports gpioA_6]

set_property -dict {PACKAGE_PIN A16 IOSTANDARD LVCMOS33} [get_ports gpioA_7]

set_property -dict {PACKAGE_PIN J15 IOSTANDARD LVCMOS33} [get_ports gpioA_20]

set_property -dict {PACKAGE_PIN H13 IOSTANDARD LVCMOS33} [get_ports gpioA_21]

set_property -dict {PACKAGE_PIN H16 IOSTANDARD LVCMOS33} [get_ports gpioA_22]

set_property -dict {PACKAGE_PIN J16 IOSTANDARD LVCMOS33} [get_ports gpioA_23]

set_property IOSTANDARD LVCMOS12 [get_ports CLK50MHZ]

set_property PACKAGE_PIN AM6 [get_ports CLK50MHZ]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks sys_clk_pin]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks sys_clk_pin]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks sys_clk_pin]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks sys_clk_pin]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks sys_clk_pin]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks -of_objects [get_pins design_1_i/system_1/inst/clk_50to16/inst/mmcme4_adv_inst/CLKOUT1]]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks -of_objects [get_pins design_1_i/system_1/inst/clk_50to16/inst/mmcme4_adv_inst/CLKOUT1]]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks -of_objects [get_pins design_1_i/system_1/inst/clk_50to16/inst/mmcme4_adv_inst/CLKOUT1]]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks -of_objects [get_pins design_1_i/system_1/inst/clk_50to16/inst/mmcme4_adv_inst/CLKOUT1]]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks -of_objects [get_pins design_1_i/system_1/inst/clk_50to16/inst/mmcme4_adv_inst/CLKOUT1]]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks -of_objects [get_pins design_1_i/system_1/inst/clk_50to16/inst/mmcme4_adv_inst/CLKOUT1]]

set_false_path -from [get_clocks -of_objects [get_pins design_1_i/system_1/inst/clk_50to16/inst/mmcme4_adv_inst/CLKOUT1]] -to [get_clocks sys_clk_pin]

set_false_path -from [get_clocks -of_objects [get_pins design_1_i/system_1/inst/clk_50to16/inst/mmcme4_adv_inst/CLKOUT1]] -to [get_clocks -of_objects [get_pins design_1_i/system_1/inst/clk_50to16/inst/mmcme4_adv_inst/CLKOUT0]]

set_false_path -from [get_clocks -of_objects [get_pins design_1_i/system_1/inst/clk_50to16/inst/mmcme4_adv_inst/CLKOUT0]] -to [get_clocks sys_clk_pin]

set_false_path -from [get_clocks clk_pl_0] -to [get_clocks -of_objects [get_pins design_1_i/system_1/inst/clk_50to16/inst/mmcme4_adv_inst/CLKOUT0]]

connect_debug_port dbg_hub/clk [get_nets CLK50MHZ_IBUF_BUFGCE]

set_property PACKAGE_PIN K19 [get_ports run_led]

set_property IOSTANDARD LVCMOS33 [get_ports run_led]

set_property IOSTANDARD LVCMOS33 [get_ports mcu_rstn]

set_property PACKAGE_PIN J17 [get_ports mcu_rstn]

set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub]

set_property C_ENABLE_CLK_DIVIDER false [get_debug_cores dbg_hub]

set_property C_USER_SCAN_CHAIN 1 [get_debug_cores dbg_hub]

connect_debug_port dbg_hub/clk [get_nets CLK50MHZ_IBUF]