近期,本届峰会组织委员会积极推进各项工作,确定本届峰会举办时间及地点,各级赞助商已招募完毕,确定了会务公司、PR公司等峰会支撑单位,演讲报告征集工作已截止,各项会务筹备工作进展顺利。

平头哥与全球顶尖的开源硬件开发社区BeagleBoard合作,推出首款单板计算机(SBC,Single Board Computer)BeagleV-Ahead。基于平头哥高性能量产RISC-V原型芯片曳影1520,开发者可以在BeagleV-Ahead单板机上运行安卓、Yocto、Ubuntu等多操作系统,探索RISC-V在AI、物联网、机器人等领域的应用创新。

「首个兼容安卓的RISC-V单板机量产上市!平头哥携手BeagleBoard联合打造」

图片来源:与非网

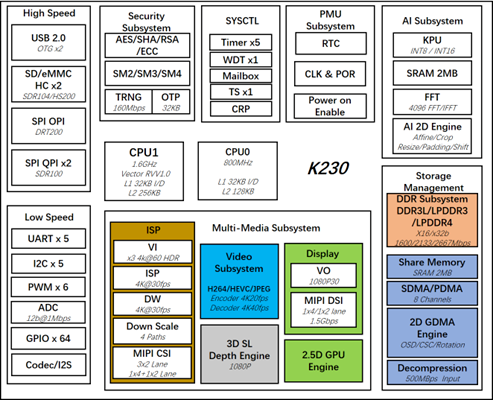

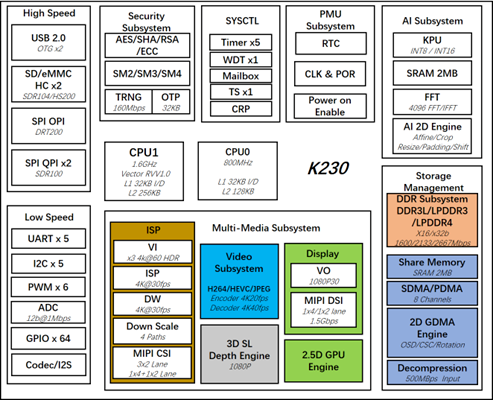

K230芯片是全球首款支持RISC-V Vector1.0标准的商用SoC,内置双核玄铁C908 CPU,主频高达1.6GHz。作为嘉楠科技 Kendryte®系列芯片中的最新一代 SoC 产品,K230 内置多个高清视频图像输入处理和智能硬件处理单元,兼顾高性能、低功耗和高安全性特点,可广泛应用于各类智能产品,如边缘侧大模型多模态接入终端、3D结构光深度感知模组、交互型机器人、开源硬件、智能制造、智能家居和智能教育硬件等众多领域。「嘉楠科技开源K230软硬件开发包 轻松实现从底层硬件到应用软件开发」

图片来源:嘉楠科技

DynamoRIO的RISC-V porting工作达到了第一个里程碑,成功在RISC-V开发板(LicheePi 4A)上跑起来了 Hello World。这是目前已知的全球首次公开展示。此项工作主要由中科院软件所(ISCAS)刘阳工程师完成。DynamoRIO是开发人员常用的性能剖析工具,目前尚未支持RISC-V架构。中科院软件所计划今年完成移植,并在2023月12月发布的如意SDK(RuyiSDK)第二版中集成,免费提供给RISC-V社区使用。「快讯:DynamoRIO 在 RISC-V 上跑起来了 Hello World」近日,RISC-V SIG发布了Eulaceura版本23H1,这是发行版的一次重大更新,新版本搭建了 linux kernel 6.1 版本内核,适用于矽速科技 LicheePi 4A 的映像也已公布。Eulaceura是首个将RISC-V 架构纳入第一级支持范围的openEuler发行,与openEuler RISC-V项目共享部分组件。「Eulaceura 版本 23H1:RISC-V架构新的里程碑」7 月 13 日,新思科技联合智东西公开课策划推出「RISC-V 内核设计与PPA优化技术公开课」,由新思科技(中国)数字芯片设计前端实现应用工程师经理闵婧、ASIP Designer 工具集资深应用工程师翟宝陆两位技术专家共同主讲,主题为《如何快速开发定制化RISC-V处理器并实现PPA目标》。

「新思科技公开课预告:如何快速开发定制化RISC-V处理器并实现PPA目标」Transfomers是自然语言处理(NLP)的重要组成部分,现在被广泛应用于图像、音频、文本等领域。该模型至关重要,因为它是CNN的补充。

该技术通过数据降噪,重建视频会议中的虚拟形象来降低5G无线网络的带宽。大型语言模型(LLM)人工智能被广泛认为是一种重要的生产力工具。大模型有没有天花板?人们正在探索中。Efabless人工智能开源硅设计系列挑战吸引了全球LLM人工智能芯片设计开发者的关注。与该系列的第一个挑战赛一样,第二届的参赛者将使用人工智能工具从自然语言提示中生成Verilog代码。

大赛作品提交截止日期为2023年9月7日,并于2023年9月14日宣布获奖者。啄木鸟半导体科技非常荣幸地在ISEDA 2023(International Symposium of EDA)国际研讨会上展示了啄木鸟半导体科技的突破性进展。啄木鸟的革命性解决方案Lockstep-FV是一款尖端的自动形式工具,专为RISC-V CPU验证设计,代表了硬件验证领域的重要里程碑。通过减少形式验证的开销,Lockstep-FV赋予了设计和验证团队提高生产力、提高效率和加快上市时间的能力。

「啄木鸟科技Roger Sabbagh:端到端的自动化形式验证」

“RISC-V势不可挡”,暌违中国数年的RISC-V主要发明人、SiFive共同创办人兼首席架构师Krste Asanovic教授,在近日刚刚圆满落幕的2023 SiFive RISC-V中国技术论坛北京、上海、深圳三地巡回演讲时,始终强调了这一核心思想。

「RISC-V成“垂直半导体”时代必选项!近2500人共同关注SiFive中国技术论坛」法国的Tiempo Secure最新的TESIC专为iSIM、eSE、支付、UWB、数字身份证、物联网安全和移动应用处理器等应用而设计的安全元件,已成功通过SERMA CC EAL5+AVA VAN.5安全测试,进一步展示了Tiempo独特的安全专业积累。Tiempo Secure利用其在微电子安全IP领域的长期专业知识,部署了具有RISC-V核心的TESIC设计。这种新的IP对任何安全元件都至关重要——这是构建经认证的安全组件的基本技术,以保证物联网有线或无线通信、iSIM、信任根安全设计和HSM的安全。

「Tiempo Secure最新的TESIC RISC-V套件已通过SERMA CC EAL5+评估测试」

近日,Imperas和Cadence介绍了为日本NSITEXE开发汽车和AI RISC-V处理器IP的验证平台的详细流程。

双方为NSITEXE Akaria处理器IP制定了全面的验证流程,其中包括NS72,这是一款带有RVV矢量扩展的64位RISC-V处理器—专为母公司日本电装开发汽车、AI芯片和其他安全键嵌入式芯片而设计。「Imperas透露AI RISC-V适量处理IP验证细节」AnalogLamb的Polos系列开发板近日推出三款低成本产品,均由沁恒的RISC-V微控制器供电,起价1.99美元。

引起我们注意的是,AnalogLamb在Linux Gizmos的产品公告中解释道:“Polos CH32Vxx RISC-V转接板是基于32位RISC-V核心的互连MCU,具有硬件堆栈区域和快速中断进入特性。与标准RISC-V相比,中断响应速度大大提高。「AnalogLamb推出RISC-V Polos开发板,起售价仅1.99美元」

OpenArkCompiler Weekly(第169期·2023-07-09)

开源开发工具周报OSDT Weekly(第210期·2023-07-12)