3月14日,在2024玄铁RISC-V生态大会上,阿里巴巴达摩院院长张建锋表示,随着新型算力需求激增,RISC-V发展迎来蝶变,即将进入应用爆发期。他表示,达摩院将持续加大RISC-V的研发投入和生态共建,做RISC-V社区的贡献者、推动者。

芯原股份近日宣布先楫半导体的RISC-V芯片HPM6800系列新一代数字仪表显示及人机界面系统应用平台采用了芯原的高性能2.5D图形处理器 (GPU) IP。

「芯原业界领先的嵌入式GPU IP赋能先楫高性能的HPM6800系列RISC-V MCU」近日,西门子EDA与芯来科技宣布达成战略合作:西门子EDA的Tessent™ Enhanced Trace Encoder增强型追踪编码器解决方案已全面支持芯来RISC-V处理器内核,该解决方案将为选择芯来科技RISC-V CPU IP的客户提供一种实时监控CPU程序执行的机制。它将在SoC层面对程序执行(指令跟踪)以及可选的加载和存储指令中的数据(数据跟踪)进行编码,以高度压缩的格式输出跟踪,使用户在复杂的异构设计中显著提高生产效率。

「芯来科技携手西门子EDA,推进RISC-V CPU Trace完整解决方案」

在经历了艰难的2023年之后,SiFive的情况可能会好转,该公司预计人工智能将在2024年推动强劲的收入增长。

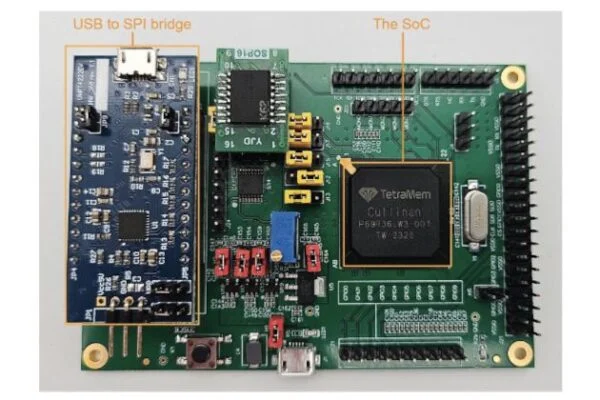

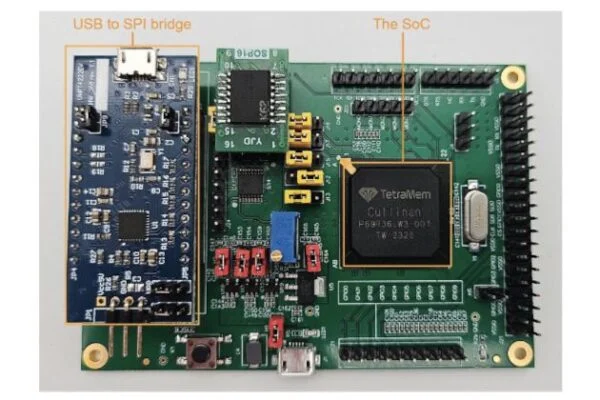

根据彭博社本周获得的文件,这家硅谷新贵的反弹将由为人工智能服务器设计的第二代处理器推动,或者说这是该公司所希望的。「泄露的文件暗示谷歌可能在下一代TPU中使用SiFive RISC-V核心」TetraMem是一家专注模拟-RRAM计算处理器架构的初创公司,TetraMem与Synopsys合作开发了一种模拟内存AI计算加速器SoC,该SoC名为Cullinan。

该芯片围绕RISC-V架构构建,并由模拟内存计算技术提供动力。「TetraMem发布模拟ReRAM SoC——Cullinan」

图片来源:eeNews

欧洲云提供商Scaleway自豪地推出一系列RISC-V服务器,再次标志着其对创新的承诺以及对培育未来技术的奉献。

本土RISC-V CPU IP领军企业——芯来科技正式发布针对信息安全的超低功耗嵌入式RISC-V处理器CPU IP——NS100系列内核,主要针超低功耗下的信息安全应用。此次发布的NS100在已有的NS300和NS600基础下,完成了芯来科技NS全系列的拼图。「芯来科技发布最新NS100内核IP,完善全系列信息安全内核布局」

Semidynamics发布了名为Configurator的新工具,支持其公司可配置的、可定制的RISC-V处理器核心。

Configurator使用数十个已经由Semidynamics验证过的模块,客户可以使用该工具在几个小时内从数千种可能的变体中快速获得可行的核心设计。

近日,本土专业RISC-V处理器IP及解决方案公司芯来科技与专业虚拟仿真工具及解决方案公司杭州芯芒科技共同宣布达成战略合作。

芯芒科技的Mosim系列仿真验证工具将全面支持芯来全系列RISC-V处理器IP,帮助下游芯片公司尤其是大型SoC设计团队快速创建整芯片&系统虚拟原型,并提供一系列高效的软硬件开发工具,助力客户产品加速上市,共同促进RISC-V产业的发展和变革。「协同创新 | 芯来科技携手芯芒科技共促RISC-V CPU系统功能和性能仿真解决方案」欧盟领导人最近启动了几项举措,以促进基于RISC-V的芯片的开发,以回应成员国对半导体依赖外国公司的担忧。最近的全球芯片短缺扰乱了供应链,凸显了芯片主权的重要性,加剧了这种担忧。「欧盟应用RISC-V实现自主可控」

https://www.design-reuse.com/news/55796/european-union-chip-sovereignty-risc-v.html

——Design & Reuse

瑞典的Imsys开发了RISC-V处理器核心,是开发太空人工智能加速器项目的一部分。

Imsys指出,欧盟的总体战略是加大对开放RISC-V技术的投资,以加强技术独立性,刺激经济增长,加快创新步伐,Imsys目前正在申请欧盟项目。「Imsys开发RISC-V核心,将目光投向太空中的人工智能」

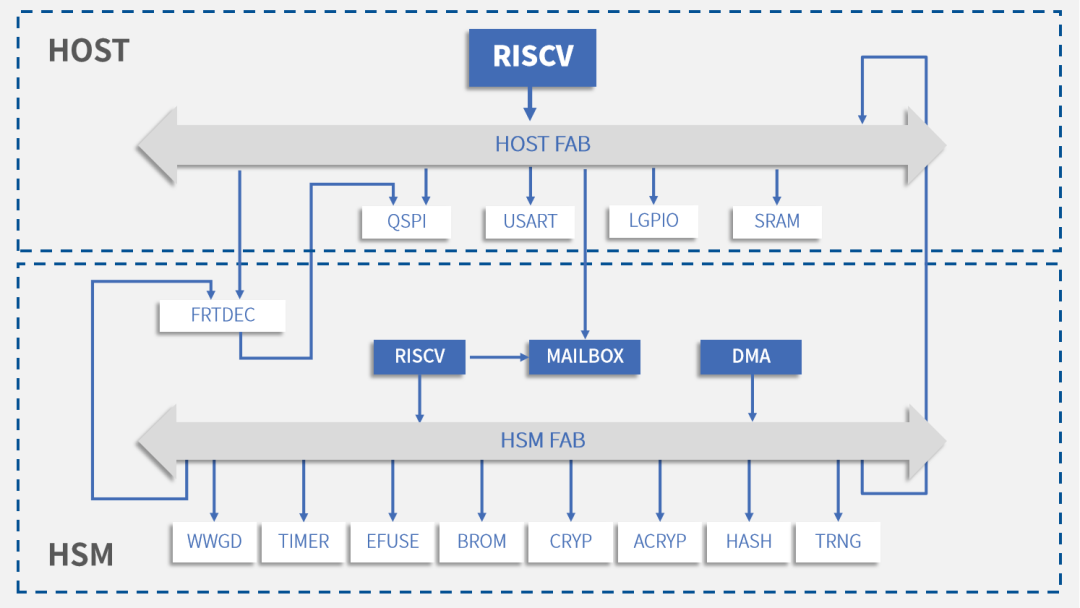

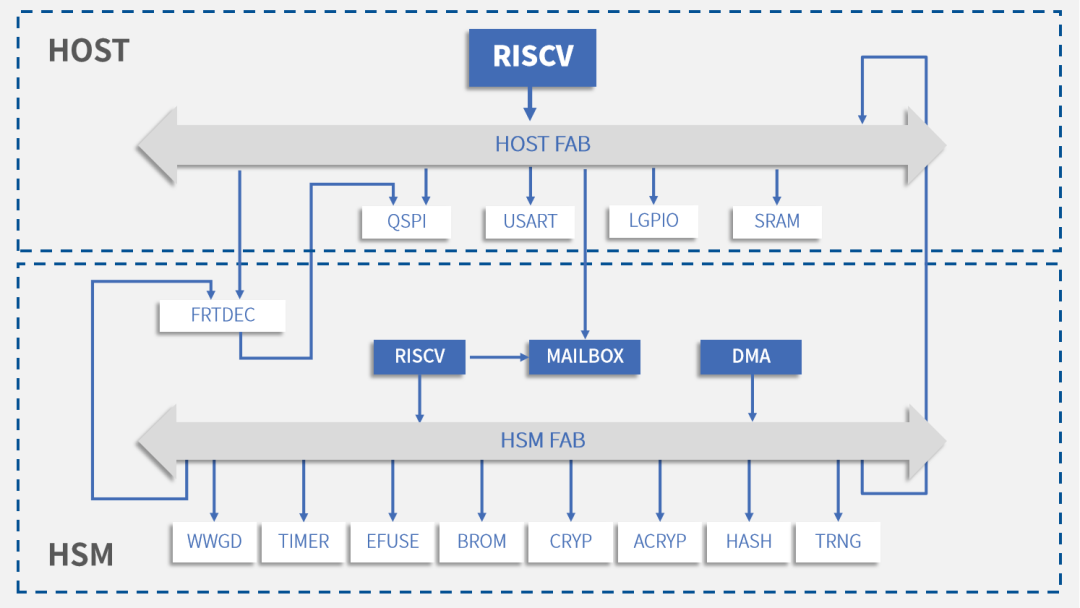

此次芯来科技发布的HSM子系统,作为针对信息安全的完整解决方案,旨在帮助各类场景对于芯片层面信息安全的需求。HSM是硬件安全模块(Hardware Security Module)的简称。HSM通过验签和加解密等功能来保护系统认证所需要的密钥和敏感数据,同时可以为在线升级、固件升级等提供安全保护,以确保传输消息和数据的机密性和可靠性。

「芯来科技正式发布HSM安全子系统方案,进一步拓展RISC-V应用领域」

图片来源:芯来科技

Tiempo Secure的TESIC RISC-V安全IP在GlobalFoundries(GF)22FDX®平台上与MRAM一起流片验证。安全IP还通过了ITSEF SERMA实验室的CC EAL5+AVA_VAN.5安全评估测试。GF行业领先的22FDX(22nm FD-SOI)平台拥有超低功耗存储器、卓越的能效和嵌入式MRAM技术。

「Tiempo Secure的TESIC RISC-V 安全IP在GlobalFoundries的22FDX工艺节点上验证成功」

Altera正式独立,CPU和FPGA最终还是“分手”了RISC-V从愿景到现实:Karel Masarik访谈

OpenArkCompiler Weekly(第203期·2024-3-10)

开源开发工具周报OSDT Weekly(第244期·2024-3-06)

https://mp.weixin.qq.com/s/6pkltR1oUQax2MolocXxWw