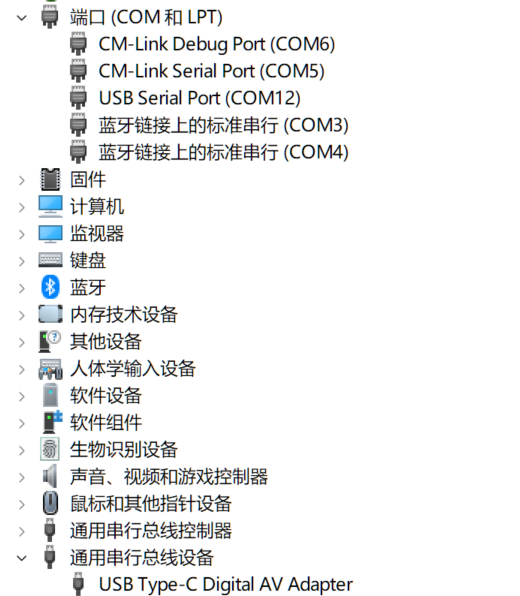

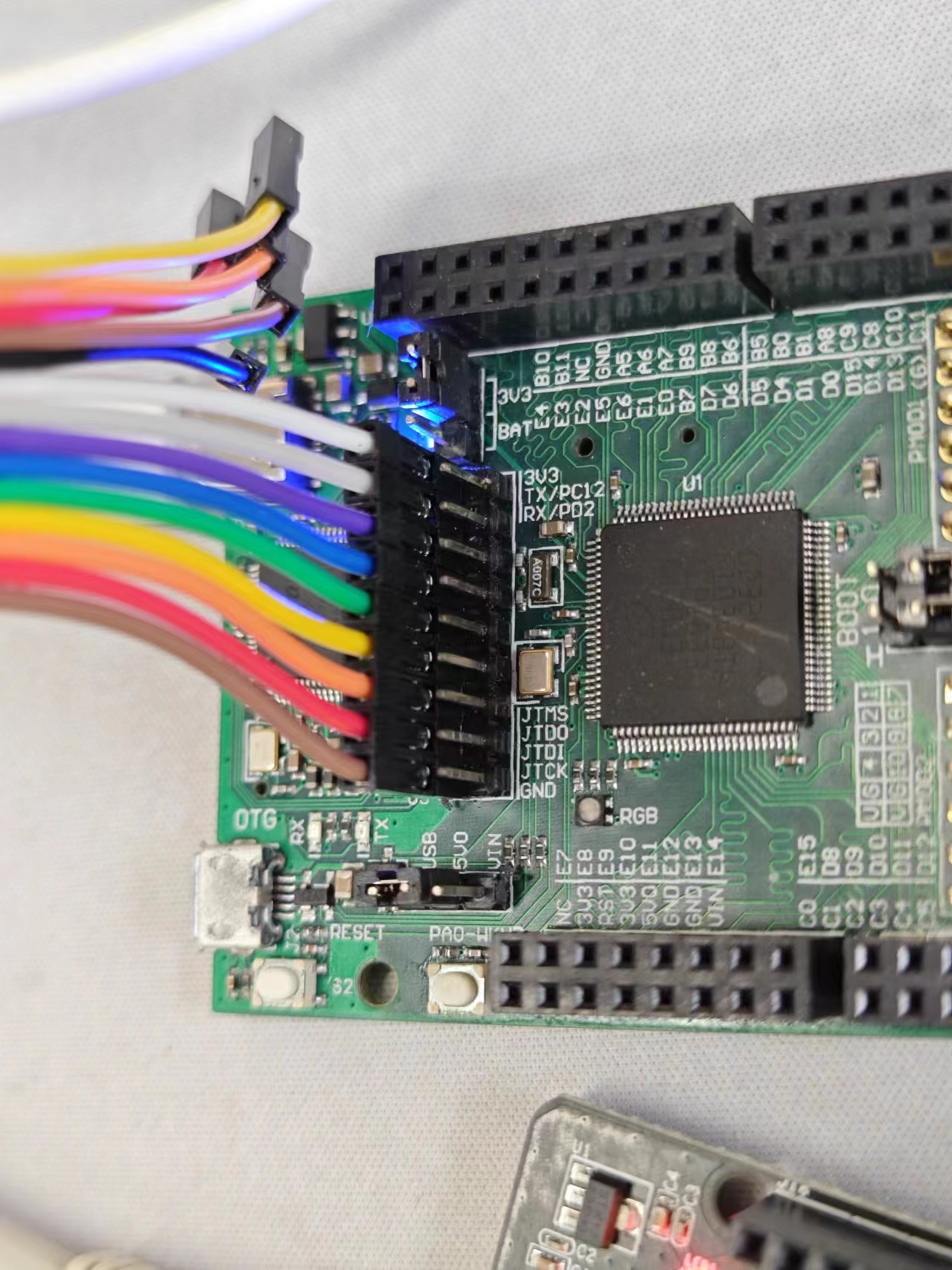

使用RV_STAR上集成的蜂鸟调试器,连接到CM32M433R-START开发板上的jtag端口,使用cjtag协议来调试MCU,但在openocd配置文件里开启nscan1_mode后,开启openocd连接到板子时,会报错,连接不上。

(我使用普通的4线jtag协议时,即nscan1_mode off,可以正确连接开发板,读出TAP ID等信息,在软件配置和接线上应该大致无错。保持接线不变,仅在openocd配置文件里开启nscan1_mode后,openocd不能连接板子读出TAP ID,报错all read zero。因cjtag连接已经报错,没有进行程序下载和调试的尝试。)

adapter speed 1000

adapter driver ftdi

#If you use the cJTAG interface, you should set the following options to on

#ftdi nscan1_mode off

ftdi nscan1_mode on

ftdi vid_pid 0x0403 0x6010

#ftdi layout_init 0x0030 0x001b

ftdi layout_init 0x0008 0x001b

ftdi layout_signal nSRST -oe 0x0020 -data 0x0020

ftdi layout_signal TCK -data 0x0001

ftdi layout_signal TDI -data 0x0002

ftdi layout_signal TDO -input 0x0004

ftdi layout_signal TMS -data 0x0008

ftdi layout_signal JTAG_SEL -data 0x0100 -oe 0x0100

transport select jtag

set _CHIPNAME riscv

jtag newtap $_CHIPNAME cpu -irlen 5

set _TARGETNAME $_CHIPNAME.cpu

target create $_TARGETNAME riscv -chain-position $_TARGETNAME

$_TARGETNAME configure -work-area-phys 0x20000000 -work-area-size 10000 -work-area-backup 1

#set _FLASHNAME $_CHIPNAME.flash

#flash bank $_FLASHNAME cm32m4xxr 0x08000000 0 0 0 $_TARGETNAME

init

#reset

#if {[ info exists pulse_srst]} {

# ftdi_set_signal nSRST 0

# ftdi_set_signal nSRST z

#}

#halt

cjtag,开启nscan1_mode,不能正确连接,不能读出tap id等信息,在debug level 2时,打印log如下:

E:\Cui\SEC\FPGA_debug\my_riscv555\Nuclei\OpenOCD\2024.02.28\bin>openocd -f E:\Cui\SEC\FPGA_debug\my_riscv555\Nuclei\OpenOCD\2024.02.28\scripts\target\cm32m4xxr.cfg

Open On-Chip Debugger 0.11.0+dev-02405-ga383d1d03 (2024-02-28-02:57)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : libusb_open() failed with LIBUSB_ERROR_NOT_FOUND

Info : no device found, trying D2xx driver

Info : D2xx device count: 2

Info : Connecting to "(null)" using D2xx mode...

Info : clock speed 1000 kHz

Info : cJTAG timing not satisfied please check constraint or underclocking.

Info : cJTAG timing not satisfied please check constraint or underclocking.

Error: JTAG scan chain interrogation failed: all zeroes

Error: Check JTAG interface, timings, target power, etc.

Error: Trying to use configured scan chain anyway...

Error: riscv.cpu: IR capture error; saw 0x00 not 0x01

Info : cJTAG timing not satisfied please check constraint or underclocking.

Warn : Bypassing JTAG setup events due to errors

Error: dtmcontrol is 0. Check JTAG connectivity/board power.

Warn : target riscv.cpu examination failed

Error: dtmcontrol is 0. Check JTAG connectivity/board power.

Error: dtmcontrol is 0. Check JTAG connectivity/board power.

Info : starting gdb server for riscv.cpu on 3333

Info : Listening on port 3333 for gdb connections

Info : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

Error: dtmcontrol is 0. Check JTAG connectivity/board power.

Error: dtmcontrol is 0. Check JTAG connectivity/board power.

jtag,关闭nscan1_mode,可以正确连接,读出tap id等信息,在debug level 2时,打印log如下:

E:\Cui\SEC\FPGA_debug\my_riscv555\Nuclei\OpenOCD\2024.02.28\bin>openocd -f E:\Cui\SEC\FPGA_debug\my_riscv555\Nuclei\OpenOCD\2024.02.28\scripts\target\cm32m4xxr.cfg

Open On-Chip Debugger 0.11.0+dev-02405-ga383d1d03 (2024-02-28-02:57)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : libusb_open() failed with LIBUSB_ERROR_NOT_FOUND

Info : no device found, trying D2xx driver

Info : D2xx device count: 2

Info : Connecting to "(null)" using D2xx mode...

Info : clock speed 1000 kHz

Info : JTAG tap: riscv.cpu tap/device found: 0x13080a6d (mfg: 0x536 (Nuclei System Technology Co Ltd), part: 0x3080, ver: 0x1)

Info : [riscv.cpu] datacount=4 progbufsize=2

Info : Examined RISC-V core; found 1 harts

Info : hart 0: XLEN=32, misa=0x40149125

[riscv.cpu] Target successfully examined.

Info : starting gdb server for riscv.cpu on 3333

Info : Listening on port 3333 for gdb connections

Info : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

cjtag的log中,在Error前,有提到 cJTAG timing not satisfied please check constraint or underclocking.看似是时序问题导致信号错误。

个人认为这种时钟不满足应该只在调试fpga上的软核SoC可能出现,不应该出现在开发板上,而且1000KHz的TCK并不快,在JTAG调试中也使用的同样频率TCK,没有报错。cjtag调试时,把TCK降低到100KHz也会报TCK时序不满足的错。

我还使用逻辑分析仪抓取了cjtag调试时的信号,发现调试器开始时一直在 jtag状态机的IR状态上进行类似zero bit scan的操作,但按照规范,这种操作应该在DR状态上进行。