NICE接口介绍

在蜂鸟E203处理器核中,使用了NICE(Nuclei Instruction Code Extension)接口进行的协处理器扩展,详情请访问蜂鸟E203 SoC配套文档。

蜂鸟E203协处理器参考示例

01

示例协处理器的实现需求

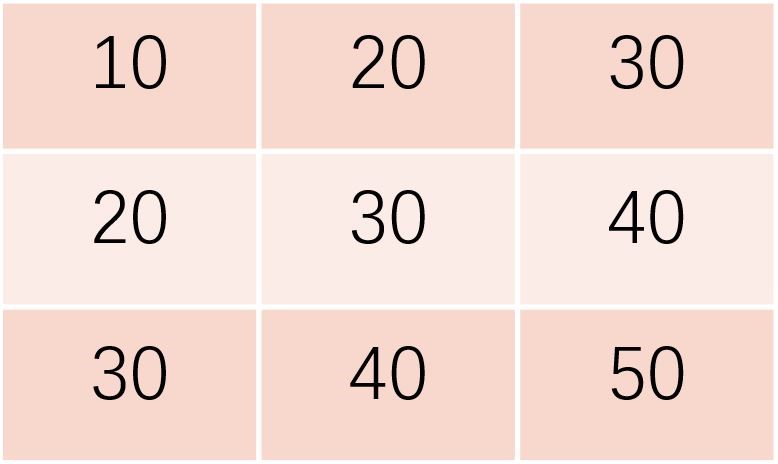

假设有一个3行3列的矩阵按顺序存储在存储器中,矩阵的每个元素都是32位的整数,参考示例如图1所示。需要对该矩阵进行如下操作。

· 计算逐行的累加和,由于有3行,因此可以得出3个累加的结果,分别是Rowsum1,Rowsum2,Rowsum3。

· 计算逐列的累加和,由于有3列,因此可以得出3个累加的结果,分别是Colsum1,Colsum2,Colsum3。

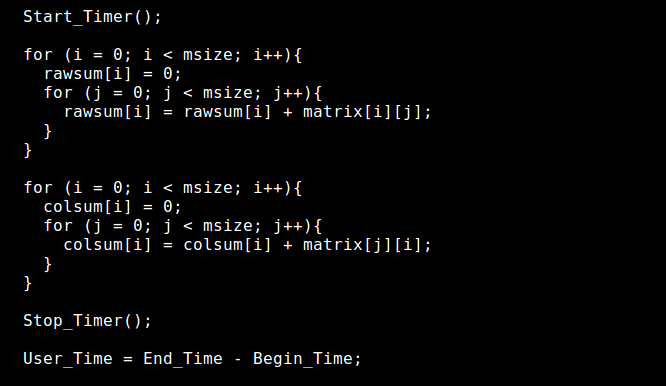

如果采用常规的程序进行计算,则需要采用循环方式,按行读取各个元素,然后将各个元素相加得到各行的累加和,然后再采取循环方式,按列读取各个元素,然后将各个元素相加得到各列的累加和,如图2所示。

图1 3×3矩阵

图2 C语言程序计算矩阵行列累加和

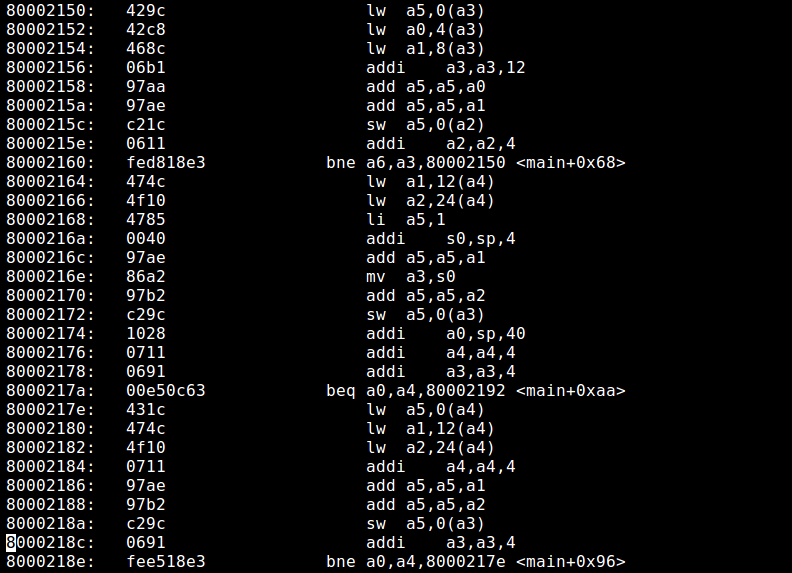

这种程序转换成为汇编代码需要消耗较多的指令条数,如图3所示。理论上它需要完整的从存储器中读取矩阵元素两次,第一次用于计算行累加和,第二次用于计算列累加和,因此需要总共3×3×2次存储器读操作。此外,程序还需要指令参与循环控制,累加计算等。总计需要上百个指令周期才能完成全部运算。

图3 C语言编译所得汇编程序

02

示例协处理器的自定指令

为了提高性能和能效比,可以将此矩阵操作定义成为协处理器指令进行加速。如表1所示,定义了3条指令,分别是CLW、CSW和CACC。

03

示例协处理器的硬件实现

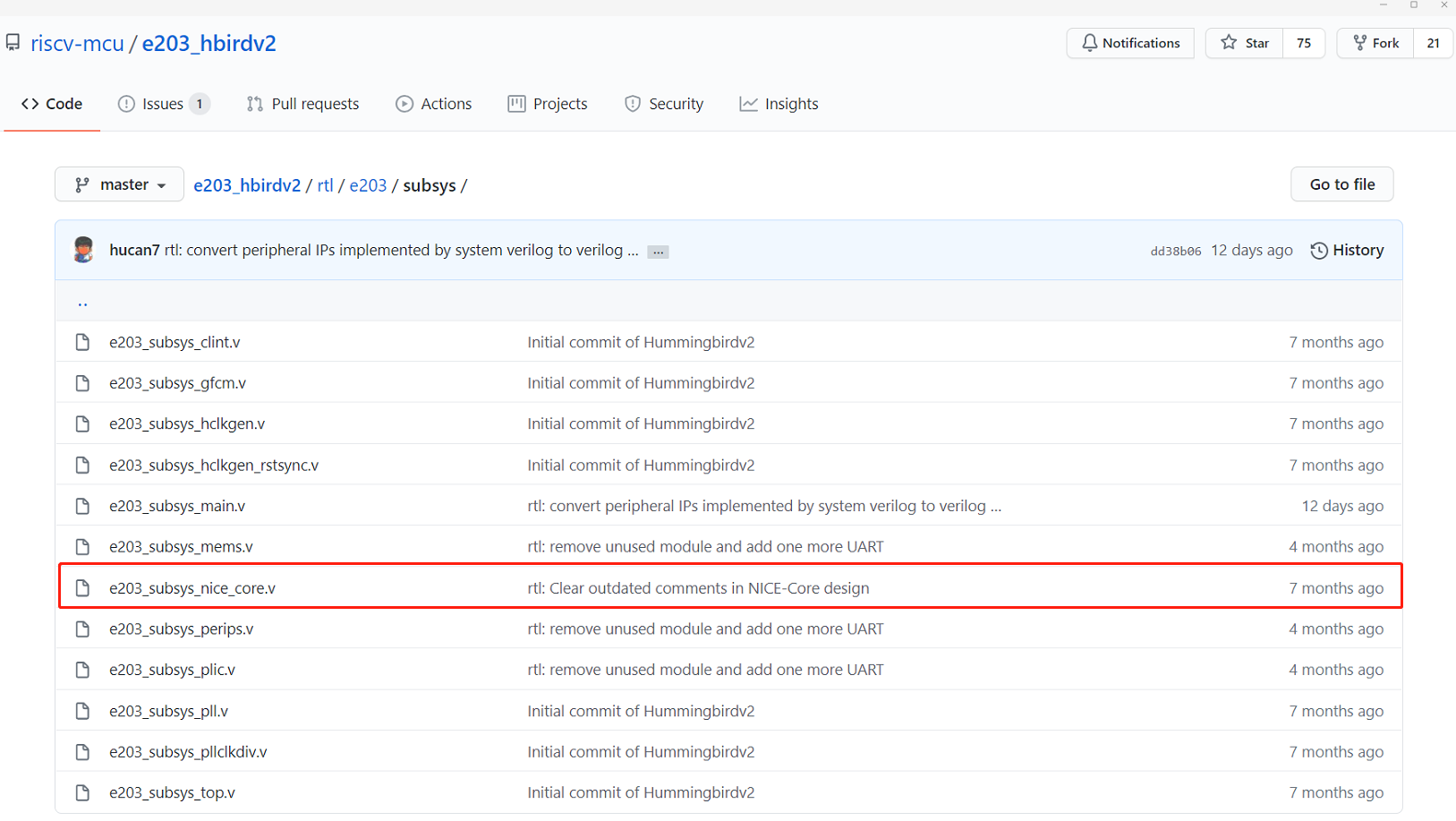

完整的实现代码可参见Github的e203_hbirdv2项目中e203_subsys_nice_core.v文件,其在 e203_hbirdv2项目中目录结构如下。

查看源代码:https://github.com/riscv-mcu/e203_hbirdv2/tree/master/rtl/e203/subsys

e203_hbirdv2

|----rtl // 存放RTL的目录

|----e203 // E203核和SoC的RTL目录

|----subsys // 存放SoC外设模块的RTL代码

|----e203_subsys_nice_core.v // 示例协处理器模块

04

示例协处理器的软件驱动及示例程序

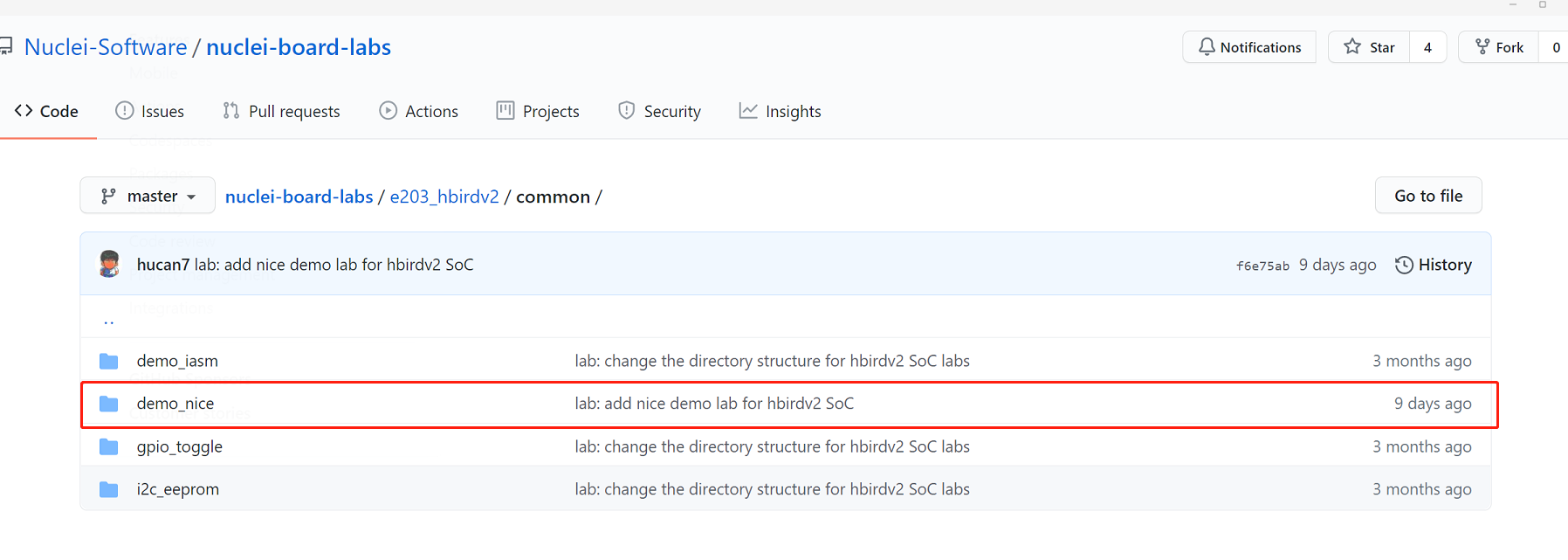

完整的实现代码可参见Nuclei Board Labs中的demo_nice例程,其在nuclei-board-labs项目中具体目录结构如下。

查看源代码:https://github.com/Nuclei-Software/nuclei-board-labs/tree/master/e203_hbirdv2/common

nuclei-board-labs // 存放Nuclei Board Labs的目录

|----e203_hbirdv2 // 存放蜂鸟E203 MCU软件示例的目录

|----common // 存放通用示例程序的目录

|----demo_nice // 存放示例协处理器实验的源代码

Nuclei Board Labs是芯来科技为其所推出的硬件平台配备的应用例程实验包。Nuclei Board Labs的源代码同时开源托管在GitHub网站和Gitee网站上,请在GitHub/Gitee中搜索“nuclei-board-labs”查看。