喜欢0次

亲爱的大神:

目前我们遇到了两个问题:

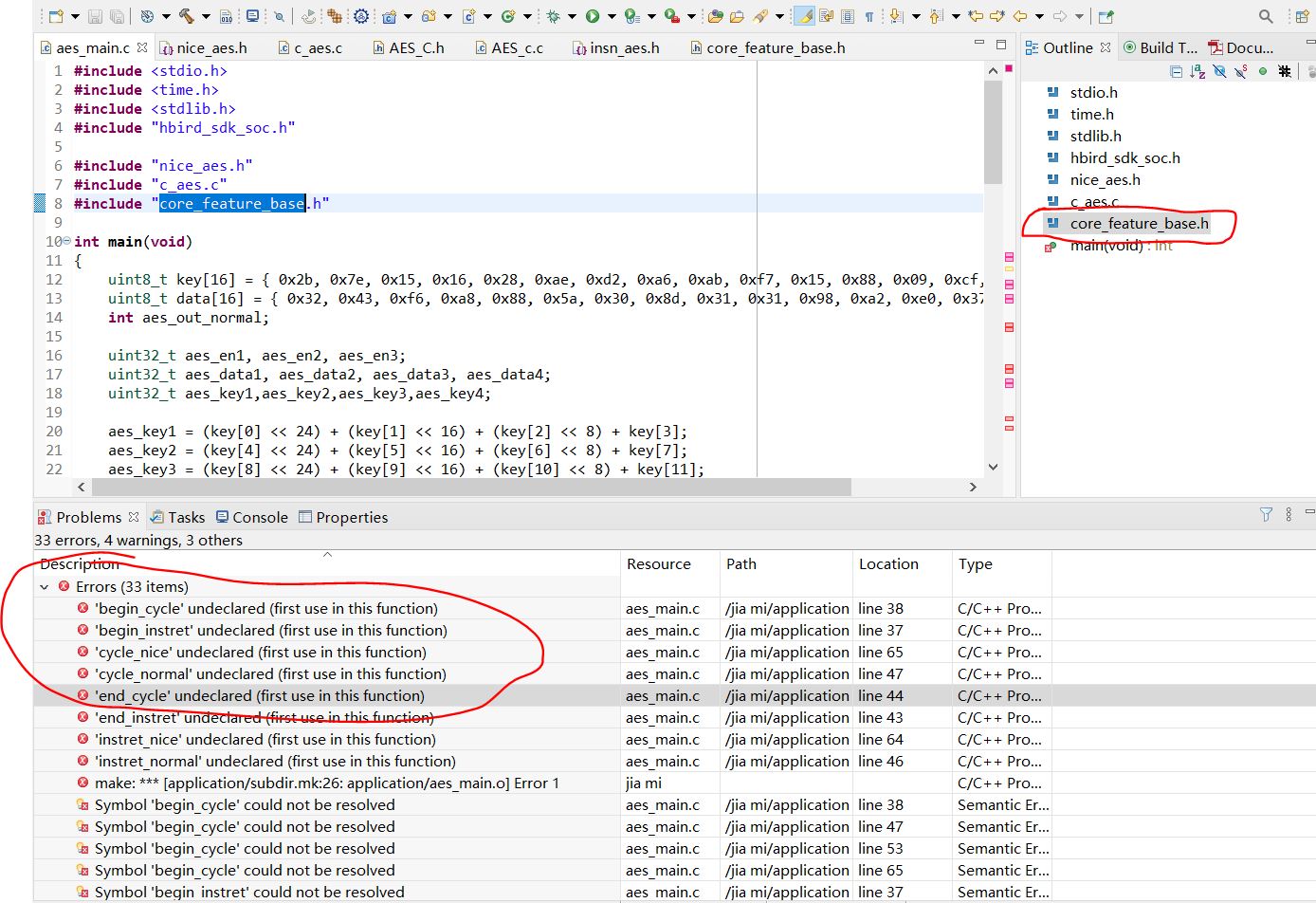

1.已经显示添加了core_feature_base.h,计数模块却依然被讲未声明;

在示例的矩阵计算代码中并未发现有地方include core_feature_base.h,却可以在编译的时候使用core_feature_base.h声明计数模块函数

2.使用nice接口的Verilog文件

可以与c语言软件程序一起添加到一个工程中吗,如果是如何添加;

还是只能Verilog文件与c语言软件程序分别单独编译烧录