队伍编号: CICC1842

由于Vivado中Block Design的友好的ui界面以及丰富的IP资源,在FPGA上实现SoC大多会采用Block Design进行设计与实现。对于基于蜂鸟e203内核的SoC设计,为了使其融合进BD设计流程,第一步需要对其总线进行配置以便于后续的SoC搭建。

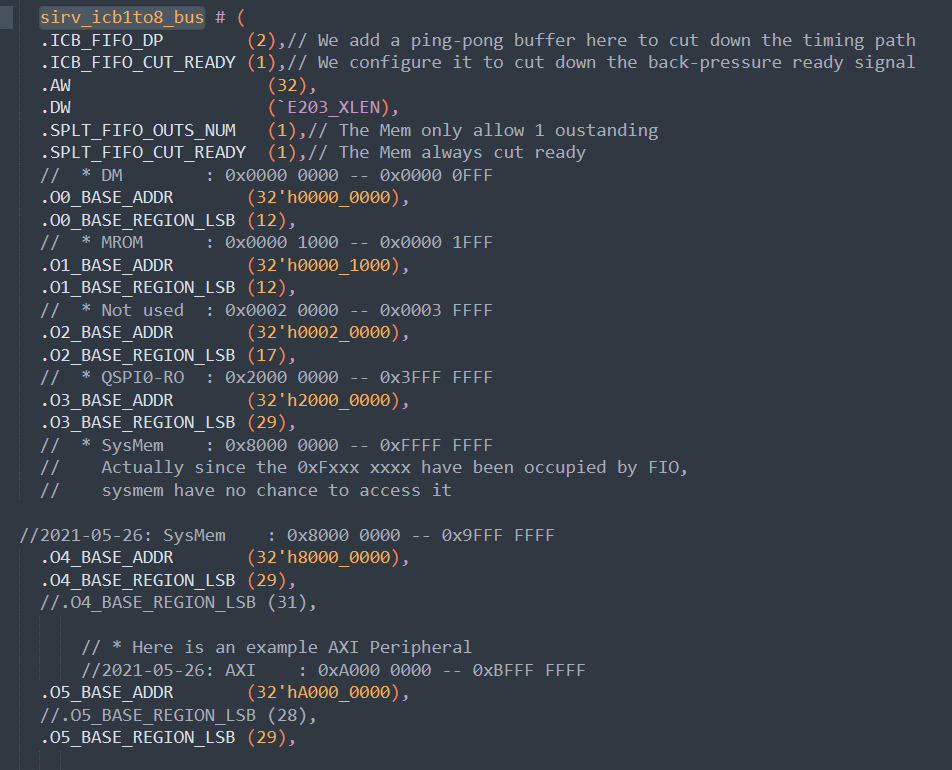

蜂鸟e203内部使用的是icb总线,这种总线协议与AXI类似,都采用了握手信号进行传输,相对易于转换;此外,在蜂鸟提供的rtl代码中也提供了icb连接AXI从设备的示例,位于/subsys/ e203_subsys_mems.v文件中,为了避免自己连接造成的错误,可以直接使用这些转换好的AXI-MASTER信号,并将其作为输入输出端口引出到顶层。此外,AXI总线的地址分配也在/subsys/ e203_subsys_mems.v文件中声明,sirv_icb1to8_bus模块中的参数定义了各个从设备的基地址与地址范围,如下图所示

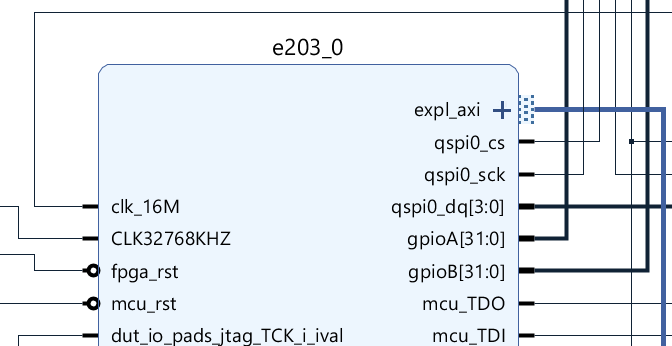

其中expl_axi即为AXI-MASTER端口,可以直接连接Vivado中提供的AXI从设备。

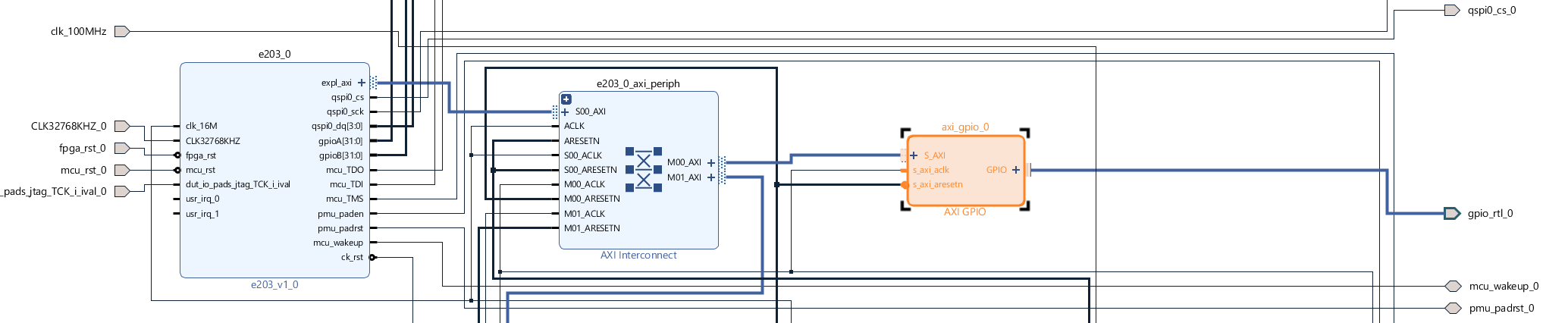

打包成功后,接下来可以利用LED对该总线是否可以正常工作进行验证,如果利用IDE编程可以控制LED的亮与灭,即可以说明AXI总线可以正确传输数据。Block Design设计如下:

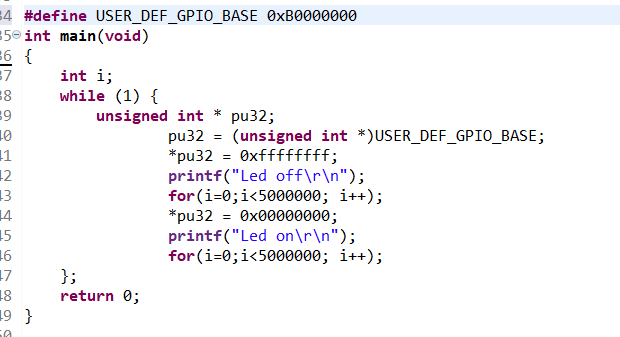

其中axi-gpio的地址设置为0xb000_0000~0xbfff_ffff,设置为全输出,并将其连接到FPGA开发板上的LED管脚。测试程序如下图所示,程序主要控制LED闪烁,如果可以在FPGA开发板上观察到LED闪烁,即可以验证AXI总线连接正常,可以进行后续操作。