队伍编号:CICC1893

队伍名称:夏芯

前文介绍了APB总线,以及基于APB总线添加外设的可能性。本篇分享基于hbirdv2的APB总线添加外设的具体过程。

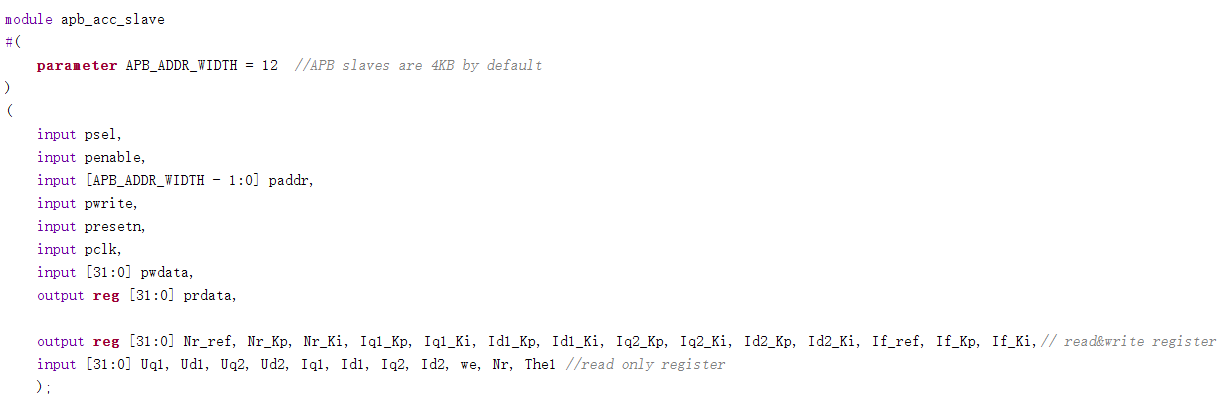

1. APB slave硬件设计

APB slave的设计首先需要按照APB总线的要求设计APB总线接口。其次,需要根据外设的需要来设计对应外设的寄存器,如定义一些只读、读写寄存器等。寄存器后级的具体算法需根据自己算法需求进行设计。下面展示一些最基本的寄存器读写设计。

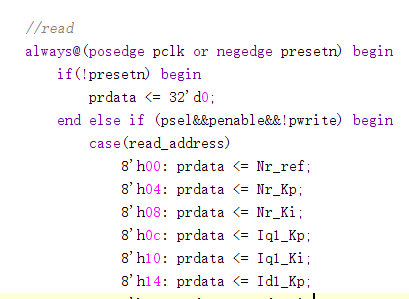

寄存器的读操作:

寄存器的写操作:

值得注意的是,相邻寄存器的地址这里分配的间隔为4,因为寄存器中数据的存取是以字节(Byte)为单位,1Byte = 8bit; 而这里因为采用32bit的数据线,故需要4个地址进行存放。

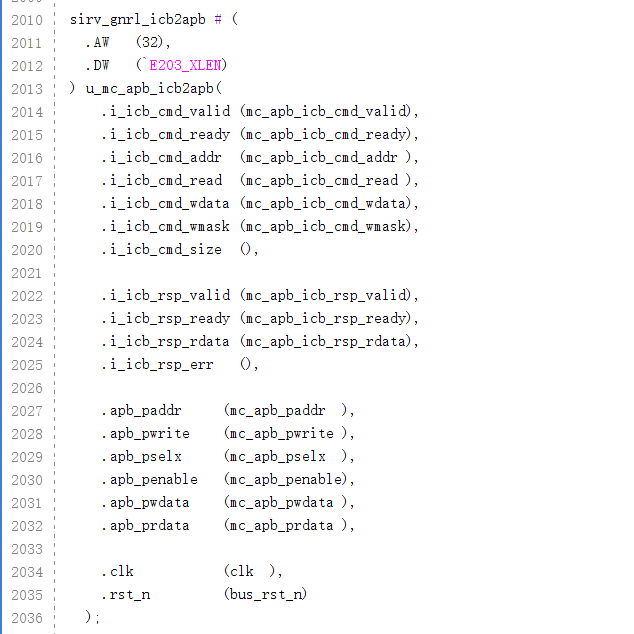

2. 添加icb2apb模块

根据之前的说明,demo SoC中APB协议的外设需再转换至ICB总线,因此在e203_subsys_perips中再添加一个icb2apb模块:

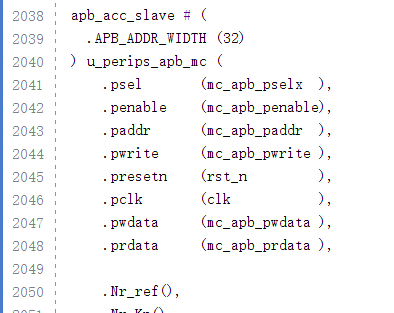

并且例化自己设计的APB slave:

3. 地址空间分配

添加完APB slave后,需对其分配一个地址空间,再这里我们给它分配为0x1004_2000 - 0x1004_2fff

4. 扩展ICB总线接口

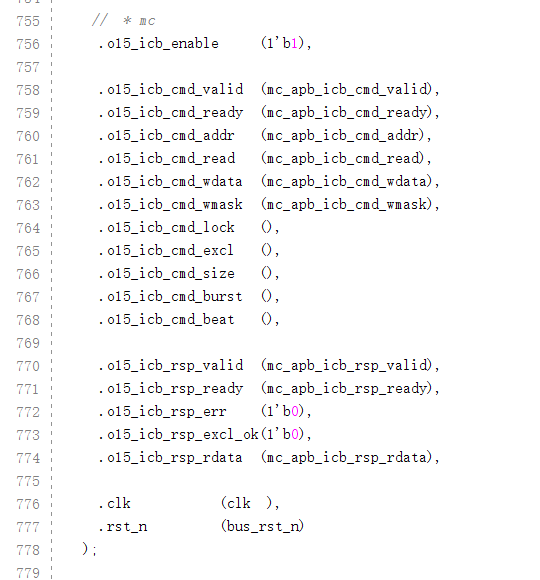

demo SoC中ICB总线预留了16个iICB的接口,其中o15未使用,这边我们直接接上icb2apb模块就可以了。

至此,基于APB总线添加外设的硬件实现基本完成。后续将介绍其软件实现。