喜欢2次

团队名称:Great Bee

大家好,本团队此次分享的内容为数据预处理软核加速模块的设计

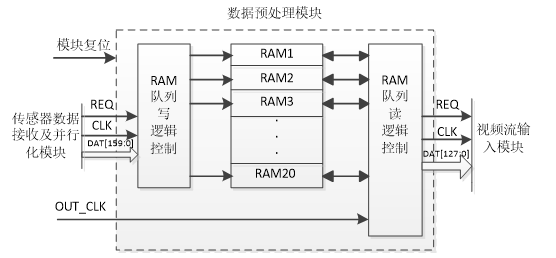

模块的主要功能是进行图像还原,即将16通道的并行数据拼接成行传输的形式。这个模块是十分必要的,如果不进行数据整理上位机收到的将是杂乱无章的数据,无法显示成一幅图像,图像恢复的过程涉及到频繁访问内存,如果用ARM处理器或上位机来实现这个过程会十分耗时,利用FPGA的并行处理技术可以轻易实现这个功能,整理后的数据传输形式会为之后的设计产生便利。模块用了20块片内双口RAM来实现数据的缓存,同时完成数据拼接操作,其预处理模块结构框图如下图

模块最后得到的信号为ddr_q、ddr_clk和ddr_wrreq。ddr_q是并行128bits图像数据,ddr_clk是RAM的出口时钟,同时引出作为下一模块的数据时钟,ddr_wrreq置高时代表有效数据。