一、团队介绍

我们的队伍名称为:我要吃火锅

队伍编号为:CICC2882

二、DDR使用

在我们的项目中,我们使用的是芯来科技的DDR200T开发板,我们通过调用板上的DDR3 IP核完成如下表的配置,配置完成后例化该DDR3,然后利用DMA和VDMA作为数据的缓冲模块,将SD卡和OV5640的数据搬运进DDR中。

|

Setting |

Value |

|

Memory Type |

DDR3 SDRAM |

|

Max. clock period |

3000ps |

|

Clock ratio |

4:1 |

|

Memory Type |

Components |

|

Memory part |

MT41K128M16HA-125 |

|

Memory voltage |

1.5V |

|

Data width |

32 |

|

Data mask |

Enabled |

|

Input clock period |

100MHz |

|

Chip Select pin |

Enabled |

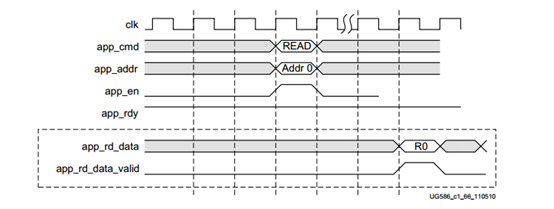

三、DDR读时序介绍

DDR3读时序如下图,由于传递地址到取出数据可能有一定延时,所以设置两个计数器分别计数传递的地址和数据的次数,只要app_rdy和app_en都处于高电平,地址计数器就会开始计数,同时地址也会增加,而只要app_rd_data_valid为高电平,数据计数器就会开始计数,当地址计数器达到预设的突发长度而数据计数器还未达到时,将进入读等待状态,当数据计数器达到时,将进入读完成状态,此时也向DMA发送读突发完成信号。当接收到DMA发来的写请求信号时,状态变为写状态。

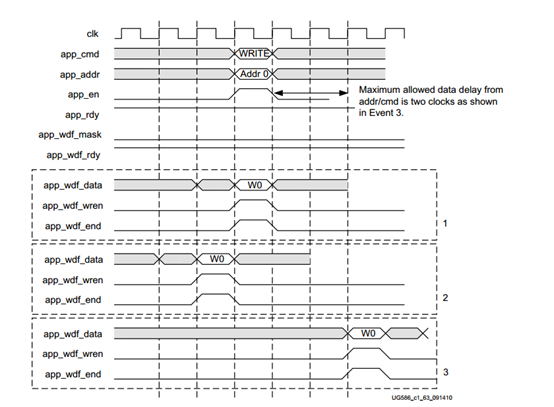

四、DDR写时序介绍

DDR写时序如下图所示,DDR3的写地址有效条件也为app_rdy为高电平,DDR3的写数据有效条件是app_wdf_rdy、app_wdf_wren和app_wdf_end为高电平,而且在写地址和写数据的对应中,并不一定存在时序完全相同的情况,写地址和写数据可能存在超前或滞后一到两个周期,因此在进行突发写时,应对地址传输完毕,但数据依然未读写完毕以及数据读写完毕,但地址未传输完毕两种情况进行考虑。具体来说,在写状态用来判断后者,也就是说一旦数据计数器达到突发值,才会结束写状态,进入写等待状态,而在写等待状态则是用来判断地址计数器是否也达到突发值,如果达到,则进入写完成状态,如果未达到,则继续计数直到满足突发值,在写完成状态向DMA发送写突发完成信号。