引言

在芯片设计复杂度日趋增长的现状下,设计一款SoC或者加速器模块所需要的设计周期和涉及风险都在不断上升。在快节奏迭代和市场的推动下,电子系统级设计(Electronic System Level , ESL)得到催生,然而ESL设计依赖于复杂的高层次建模以及庞大的数据支持,且其工具链的发展仍不是十分完善。

在现阶段的开发氛围中,软硬件协同开发是一种能够缩短开发周期,并提升总体性能的高效开发技术。分文将分享介绍硬件加速器与软件结合的协同开发方式

软硬件任务划分

我们的硬件设计涉及到MFCC模块。直接交由CPU的一次指令的五级流水线处理在麦克风数据取入上的资源耗费可以说是“大材小用”,且MFCC计算所需要的的FFT及梅尔滤波等复杂算法会极大程度上占据计算资源,这拖慢了CPU对其他程序的响应速度。

在纯软件的MFCC特征值提取计算上(参考CMSIS NN模块的MFCC计算),基于CPU的纯软件计算时间长达10秒以上。这意味着该模块需要通过硬件加速器来实现。

我们的设计将硬件加速器挂载到SoC外围总线上,自动获取麦克风的数值计算并输出数据到FIFO中,实现硬件加速。软件上利用定时器中断,率先判断该FIFO的值不为空,并且保证一次读取一个帧长(即10个周期)的数据,能够实现该FIFO内数据即写即读,数据写入不久便能取走的效果。

自定义指令集设计

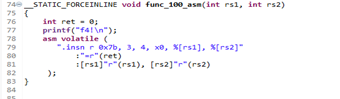

E203 SoC自带NICE协处理器接口,且支持传输自定义指令。本设计在软件层面利用C语言内联函数的方式实现了6条自定义函数的定义。

软件上传输参数需要经过取指译码执行写回等操作,而这里实现的仅需要将参数传递给协处理器,CPU只需要判定指令是否为custom类型,并将指令与RS1、RS2指令内容传递给协处理器,交由协处理器进行余下的译码以及数据的拆分。

这里给出本设计使用到的自定义指令,仅供参考:

关于自定义指令集的实现,可以参考胡老师的这篇例程,该例程在RISC-V书籍上也有提到。

欢迎提问

链接:

【声明】

由 CICC2840 队伍提供的第4篇分享,内容和图片来自小组成员。