之前试图将蜂鸟E203移植到自己的FPGA开发板,由于自己的开发板上只有一块flash,因此参考了论坛里面的帖子,附上大佬的链接:https://www.riscv-mcu.com/community-topic-id-865.html,修改了可执行文件的链接地址,以及verilog中PC的起始地址。然后将生成的.bit文件与.bin文件合并为mcs文件,load进去,在串口也打印出了相应的输出内容。当用ila查看IFU模块的两个关键输出信号时,发现和之前用testbench进行verilog仿真的输出波形有差异。

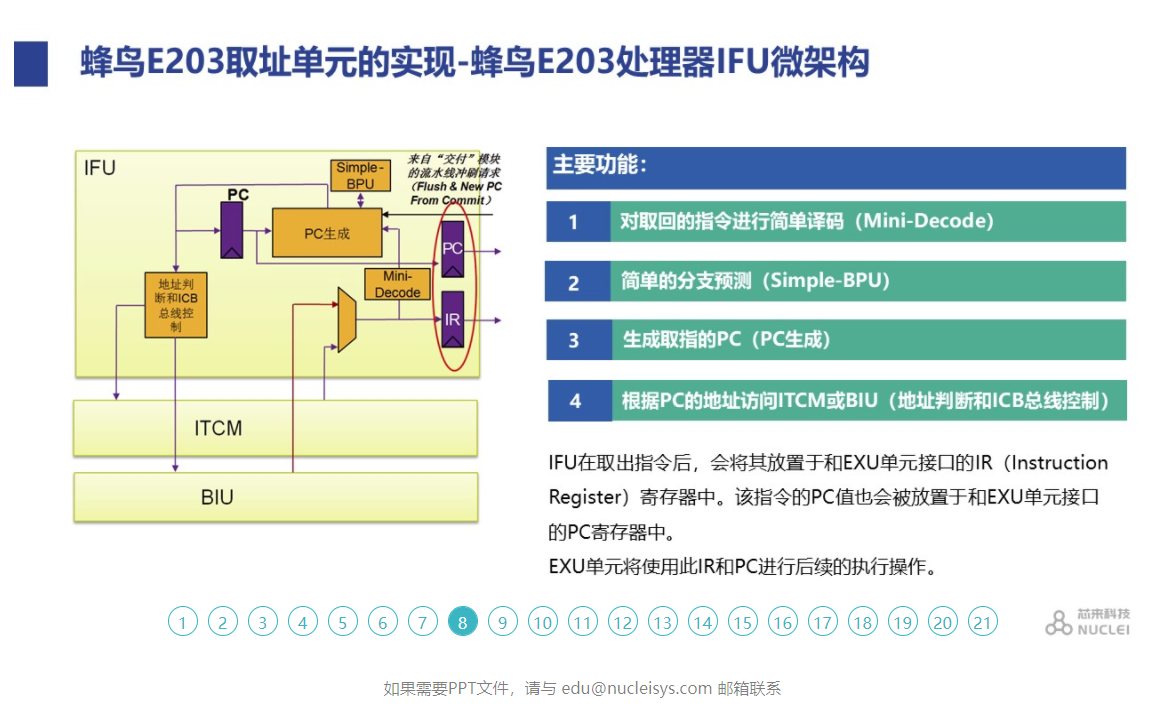

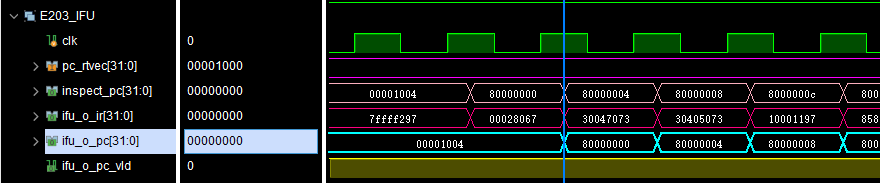

按照官网给出的ppt上上解释,如下图所示,IFU输出的pc和ir应该是对应的,也就是输出的pc位置的指令应该是ir,这和实际的仿真波形也是一致的。

图1 ppt中关于IFU输出信号的说明

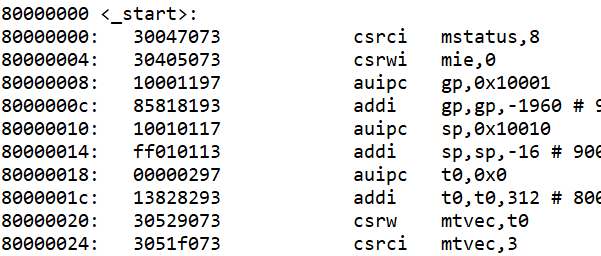

图2 反汇编文本中pc和指令(与下图中仿真波形对)

图3 verilog仿真的输出波形(pc和指令是对应的)

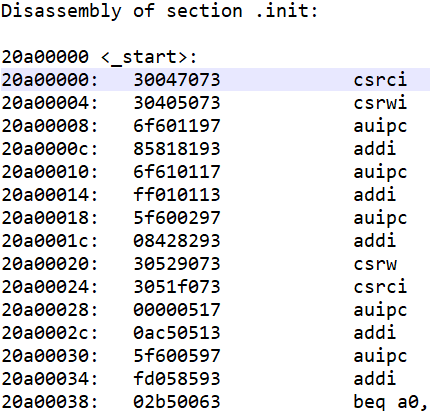

在对链接地址进行修改(主要是两处,一处为verilog中,一处为编译器链接脚本中),修改初始地址之后生成的反汇编文本,如图4所示。用ila抓取出来的信号如下图5所示:

图5 修改地址之后dasm文本内容(对照下图中的pc和ir信号)

图5 ila抓取出的IFU输出信号

从抓到的波形可以看到,ifu_o_pc是下一条指令的地址,而不是当前指令所对应的地址。也就是ifu_o_pc领先了一个周期输出,目前分析是可能由于ifu_o_pc_vld信号拉高较晚导致,verilog仿真和ila抓到的ifu_o_pc_vld变化也不是一致的。假如说ifu输出的pc是领先一个时钟周期,那么在执行跳转指令时,计算的跳转目标地址也会不准确,例如在跳转到systemInit时,就发现输出的地址不对,并且不是对齐的地址,而指令是正确的。。。很让人费解。

这种情况困扰了一天了,也没找到原因在哪儿,用ila抓信号可太累了,每次抓完信号之后,发现还要观察其他的相关信号,又得重新综合,实现。每次重新综合实现至少15分钟,太浪费时间了。希望胡老师或者有了解的小伙伴能指点一波其中的玄妙,不胜感激~~~