7月16日-18日,2025 RISC-V中国峰会主会圆满落幕。本届峰会采用“主论坛+9场垂直领域分论坛+研习会+展览展示+同期活动”的方式举行,期间吸引了众多企业宣布新产品或服务。相信此次峰会将为全球开放生态注入新的动力,也将对明确生态建设方向、促进国际技术协作发挥关键作用。

芯来科技在本届峰会中,携手合作伙伴们展示呈现了众多产品成果案例,并在主论坛、分论坛、研习会、同期活动等多个议程中为大家带来了精彩主题演讲与技术进展分享。

18日的分论坛日程中,芯来科技众多技术专家从不同的技术层面为大家分享了芯来最新技术演进与研究成果。

芯来科技高性能UX1030H处理器IP, 全面支持RVA23特性

芯来科技马越

本场演讲中马越重点介绍了芯来科技高性能UX1030H处理器IP对于RVA32特性的全面支持。随着 RVA23 Profile的正式发布,标准化虚拟化功能终于成为RISC-V官方路线图的一部分,演讲中分享了芯来在虚拟化实现中的工程方法,解析遇到的核心技术难点,并介绍我们如何系统性地解决这些问题,使RISC-V架构真正具备实用化虚拟化能力。

Nuclei Model:基于System C的Near Cycle Model

芯来科技徐子泰

演讲中徐子泰重点向大家介绍了Nuclei Model的相关特性。Nuclei Model是基于SystemC TLM-2.0开发的Near Cycle Model,旨在解决Functional Model缺乏时序信息、不支持 Profiling,以及Cycle Accurate Model性能低、建模复杂等问题。它通过引入 Timing Model 实现近似周期精度,并支持快速 Profiling、灵活扩展自定义指令及无缝集成第三方虚拟平台(VP)。

Nuclei AI Library: 使用RISC-V V扩展加速AI推理

芯来科技舒卓

本场演讲舒卓重点介绍Nuclei AI Library通过RISC-V V扩展实现AI推理加速。其中Nuclei全面支持RISC-V向量扩展(RVV 1.0),基于此实现了高效的AI算子加速;通过硬件与工具链的协同优化,在保持与上游BF16指令兼容的同时,全面支持BF16运算及转换操作,实现性能提升;同时为提升矩阵计算性能,Nuclei GCC工具链引入了定制化的VPU扩展Xxlvqmacc,

Nuclei TEE: RISC-V安全系统实践

芯来科技桂兵

演讲过程中桂兵主要分享了Nuclei TEE的RISC-V安全系统实践。随着RISC-V架构的广泛应用,信息安全正在成为比较突出的问题。演讲中介绍了在RISC-V官方还未有正式的TEE硬件安全方案的背景下,芯来科技基于开源系统在Nuclei平台上针对AP级和MCU级CPU IP做出的一些安全系统尝试与相关研究,并在最后进行了相关Demo展示。

芯来科技ASIL-B/D RISC-V IP汽车应用实现中的挑战与解决方案

芯来科技范添彬

RISC-V架构下的音频算法优化实践

芯来科技裘剑东

本场演讲裘剑东聚焦阐述RISC-V架构下的音频算法优化实践。演讲中以音频处理中核心的FIR与FFT计算为例,演示了完整的优化流程:首先利用Nuclei Studio的性能剖析功能精确定位计算瓶颈;其次通过RISC-V的Packed SIMD(“P”扩展)与Vector(“V”扩展)指令集进行深度代码优化,实现了显著的性能提升。针对极致性能场景,演讲过程中还展示了如何通过NICE/VNICE自定义指令来进一步突破性能极限。

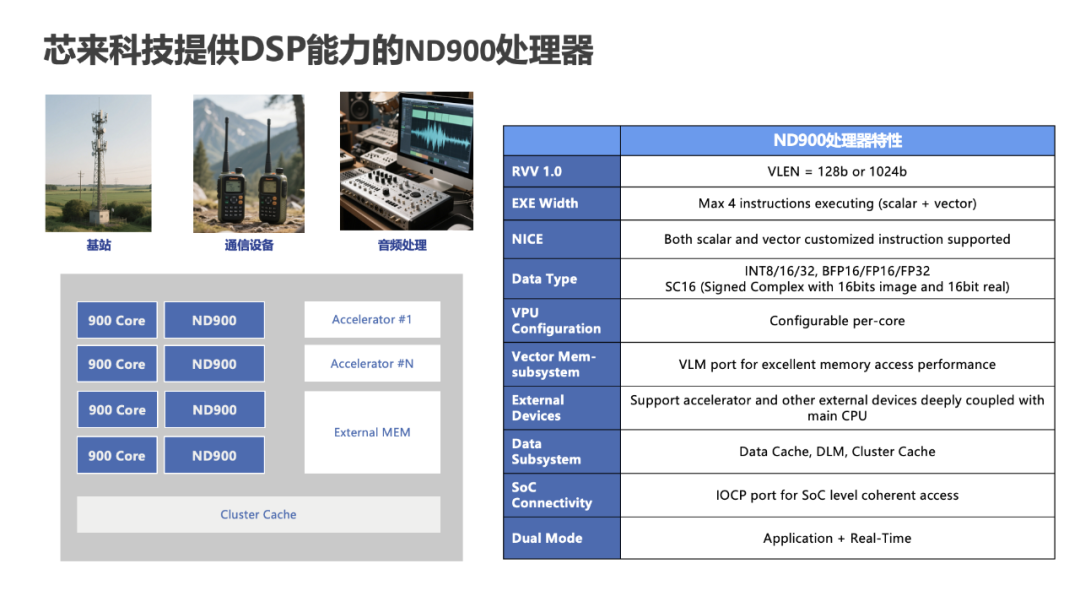

7月16日,芯来科技参加了由中移芯昇主办的RISC-V中国峰会同期活动“RISC-DSP指令集研讨会暨VDSP IP发布会”,吸引了业界广泛关注。中移芯昇在长期推动RISC-V生态建设与技术创新的过程中,识别出一个关键短板:RISC-V在高性能、实时信号处理等矢量计算场景下仍存在明显不足。为弥补这一空白,中移芯昇正式发布了面向无线通信的RISC-dsp-w标准,旨在推动RISC-V在通信、音频等典型DSP应用领域的实用化。

芯来科技马越在会上发表主题演讲《芯来助力RISC-dsp-w开拓新应用》并推出专门支持RISC-dsp-w指令集、并完全兼容RVV1.0的ND(Nuclei DSP)级别处理器产品。该产品面向通信、音频处理等高性能计算场景。芯来科技将持续深化与产业链合作伙伴的协同,加速RISC-V在无线通信、多媒体处理等垂直领域的规模化落地,推动RISC-V指令集标准、IP产品与生态应用的深度融合。

另外,在7月16日Tutorial(研习会)中,芯来科技分别在基础班、进阶班-汽车电子赛道为大家带来了精彩的分享。相信大家通过此次学习,能更加深刻地理解RISC-V的战略意义和发展机遇,并能激发RISC-V在各领域的创新潜力。

感谢各位在本次峰会中与我们展开交流探讨,芯来科技今后将继续携手产业链上下伙伴,以创新促发展,赋能产业生态,助力集成电路设计产业蓬勃发展!