在windows环境下实现移植流程,因为板子是差分时钟,在最初移植的过程中时序报告一直出错,经过调整分频设置之后可以成功生成bit文件。本文章带大家完成vivado阶段所有工作,从源代码到生成bit文件,保姆级教程,走过路过不要错过。

1.e203开源代码可在GitHub上下载

2.Vivado新建工程,先导入e203 RTL文件,

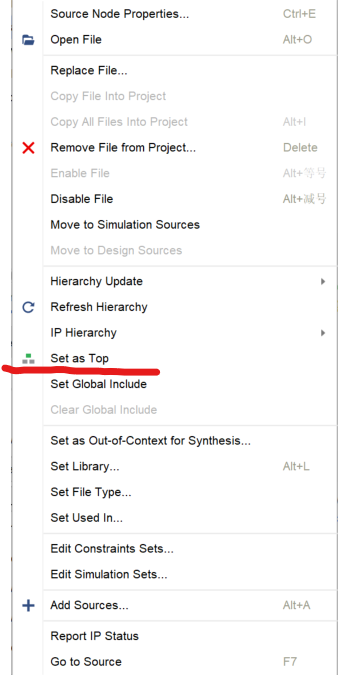

接着导入fpga文件夹中的system.v文件(e203_hbirdv2_master\fpga\ddr200t\src\system.v),并设置为顶层文件。

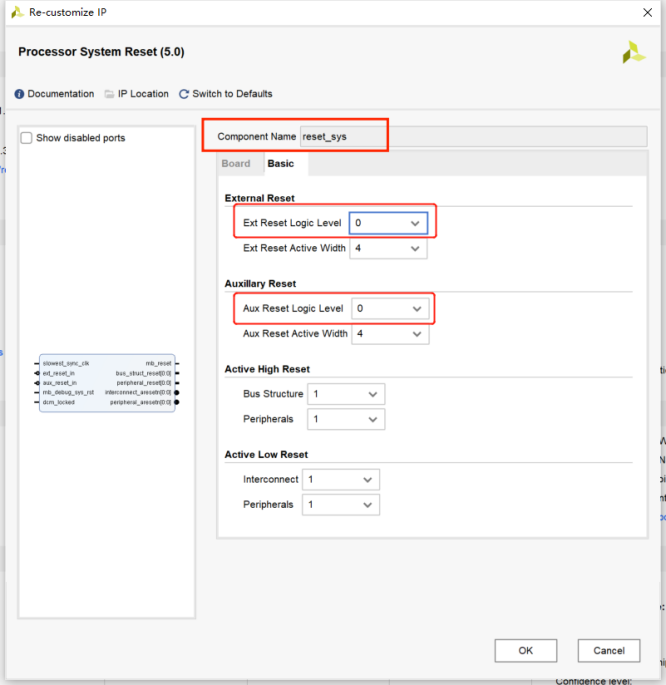

3.添加IP核,e203需要两个平台相关的IP核,用于时钟控制核复位控制,分别是Processor System Reset和Clocking Wizard(在Flow Navigator里的IP Catalog中添加),修改相应数据如下图。

Processor System Reset的ip核修改相对简单。

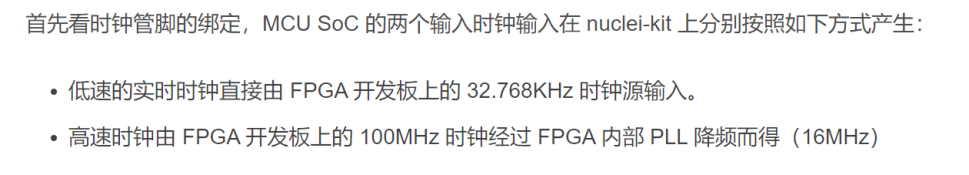

因为e203有两个输入时钟。

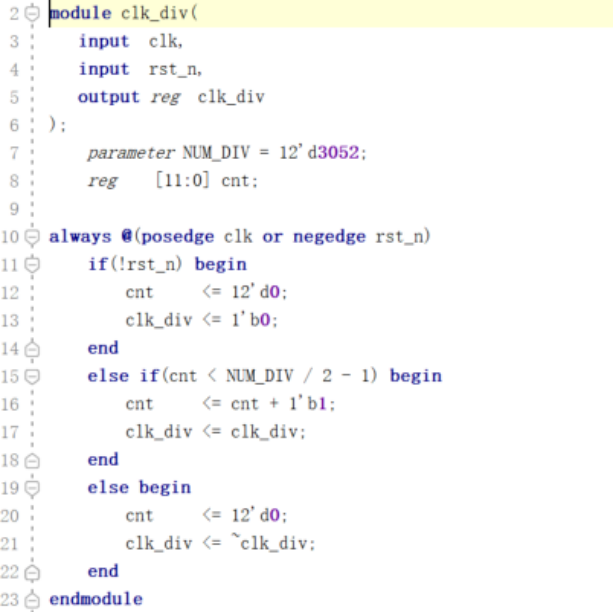

而32.768KHz超出了Clocking Wizard ip里输出分频的范围,故自己写一个counter进行分频。

在进行第二个分频Clocking Wizard ip之前,先在system.v中用原语IBUFGDS对genesys2的差分输入引出单时钟100MHz 。

再添加Clocking Wizard ip。genesys2提供的输入频率是100Mhz,输入选择单时钟源,输出只需要16Mhz。

添加完ip和自定义的分频文件之后记得在system.v中例化。

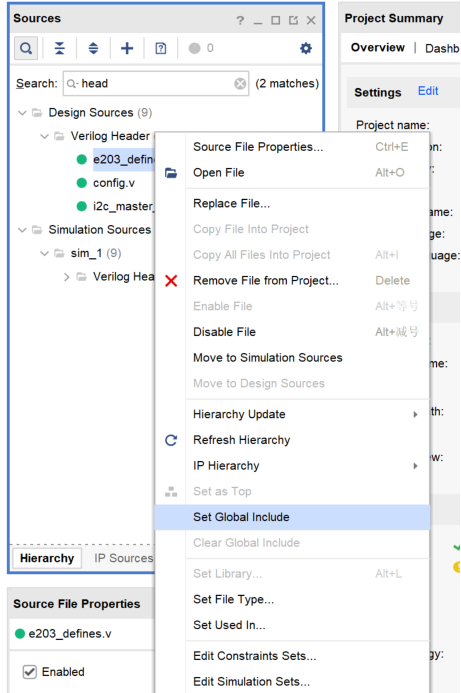

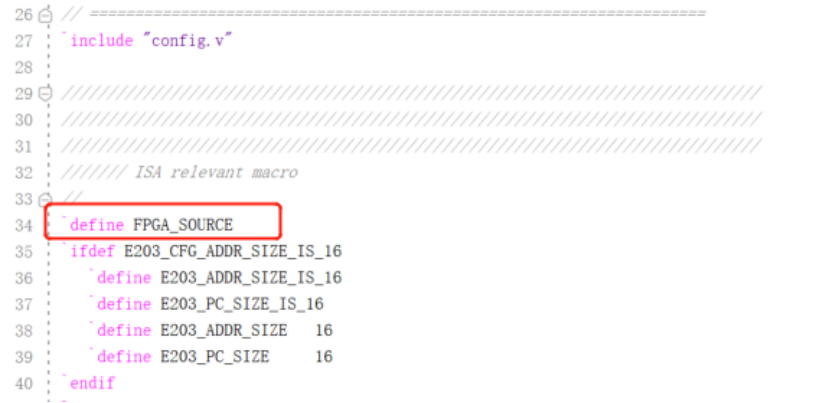

4.设置头文件与注释

添加`define FPGA_SOURCE

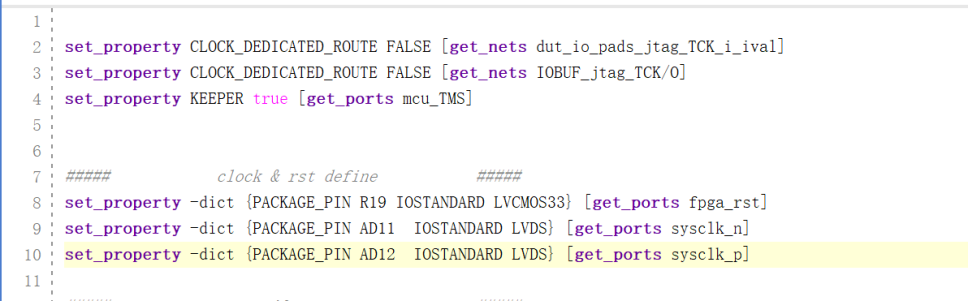

5.修改约束文件,删除不需要的引脚,保留时钟约束,注意是差分输入。

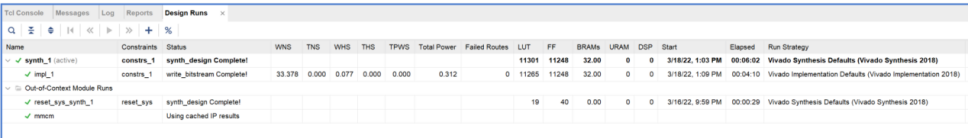

6.跑综合实现,时序如下图

成功生成.bit文件