队伍编号:CICC2663 队伍名称:太湖电子竞技小队

在编写Verilog代码时,我一般都是先在编辑器上写完,因为编辑器vscode或者notepad++可以提供语法高亮和自动补全等功能,然后用仿真器跑仿真,但是在编写过程中不可避免的会有一些语法的错误,每次跑仿真都需要修改语法错误;另外在写完一个模块之后,每次跑仿真前都需要搭建testbench,模块的实例化,这显然是很麻烦的,查阅资料发现vscode有插件可以解决上述问题,故来分享给大家。

在vscode的拓展中,输入Verilog查找如下插件:

安装完该插件后就支持了语法高亮和自动补全等功能,但是要实现自动纠错还需要安装ctags。这在该扩展的细节中有介绍,各位可以前往github自行下载。

或者网盘(链接:https://pan.baidu.com/s/1BBGw2eITE6abDMKQkcPNmw 提取码:r83z)

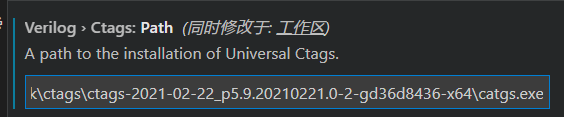

下载完成之后需要将ctags的目录添加到扩展设置中:

另外,自动纠错实际上还是用了仿真软件的工具,例如vivado、iverilog、modelsim等。下面介绍如何利用vivado的工具xvlog。

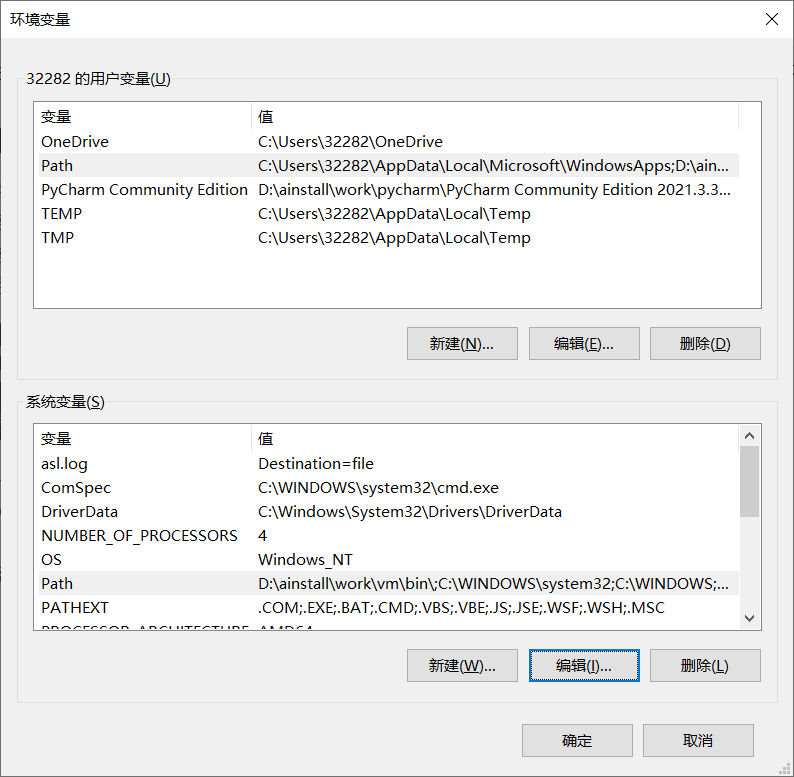

一般情况下,xvlog在vivado的安装目录下bin文件夹下,因此需要将该文件夹添加到环境变量中:

属性->高级系统设置->高级->环境变量->path

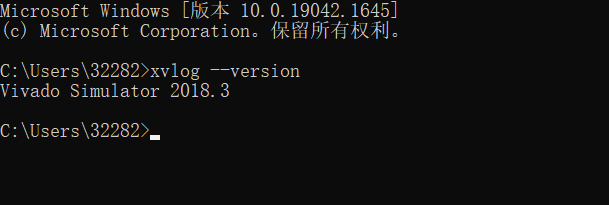

如果环境变量添加成功后,可以在cmd中查看xvlog的版本:

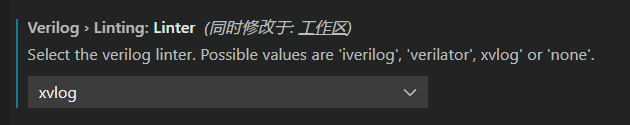

然后在该拓展设置中选择linting的工具为xvlog:

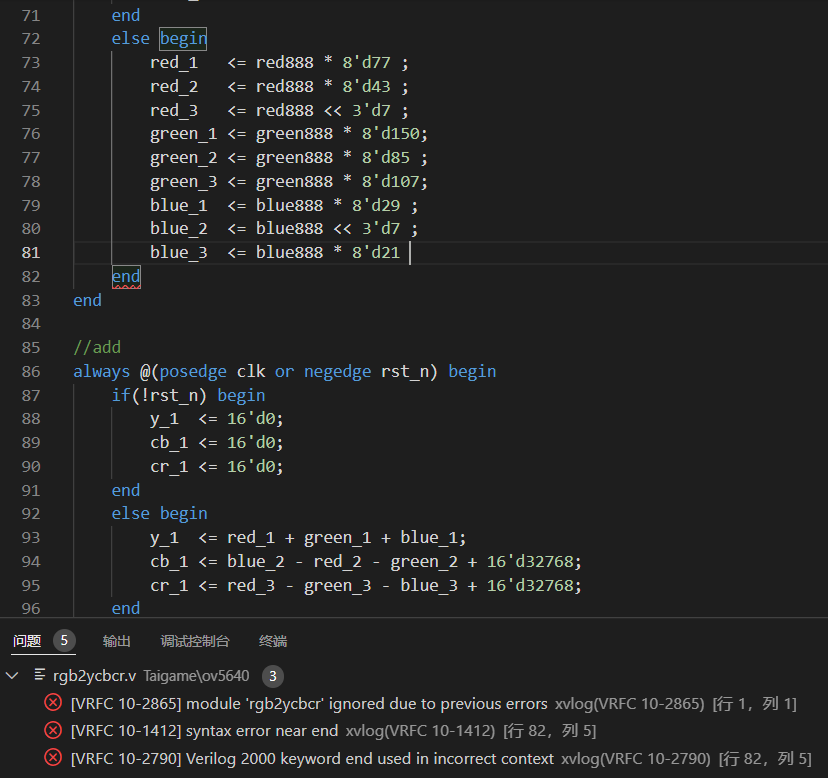

选择后,在写完Verilog代码后保存一下会自动检查语法错误,并将结果列在问题中:

比如我在81行少打了一个分号,错误会自动报出。

需要在拓展中输入Verilog_testbench,找到如下拓展:

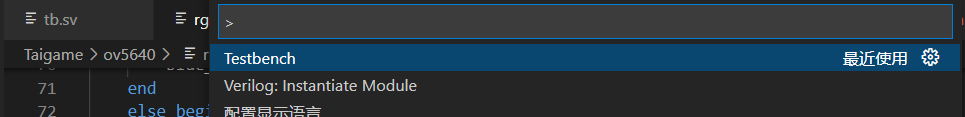

安装成功后,回到写好的Verilog代码,按住ctrl+shift+p,在弹出的搜索框里输入testbench。

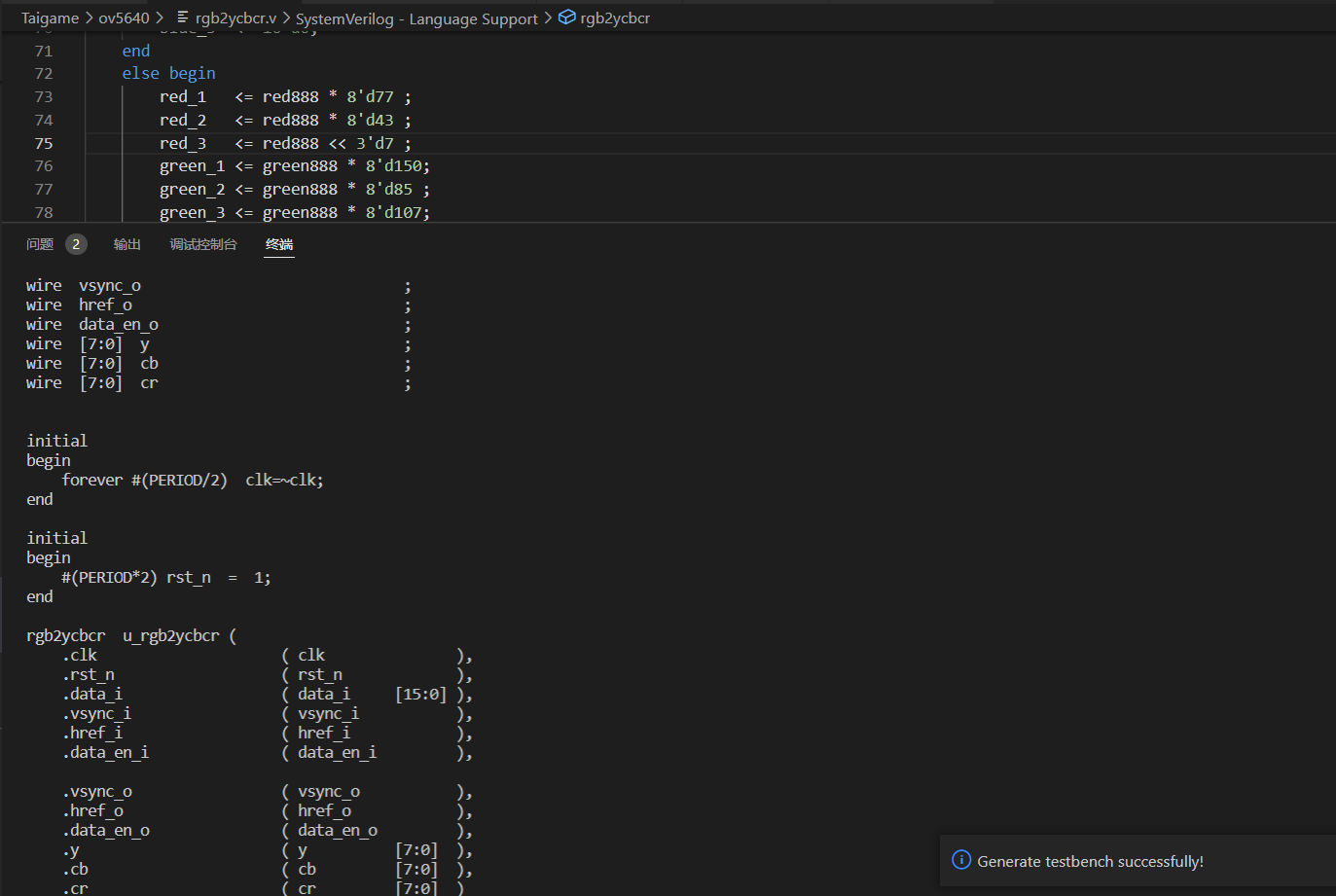

点击后会自动将当前模块的testbench生成在终端框内。

当然,本质上该插件还是通过python来实现的,因此要实现自动生成testbench还需要安装好python的环境,此处不再赘述。

希望该分享能够提高大家编写Verilog代码的效率。