创建工程

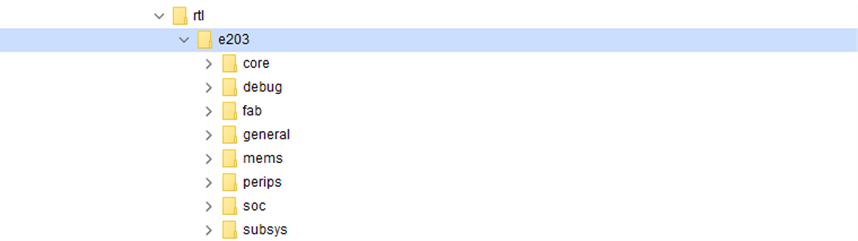

首先,创建新的工程项目,将FPGA/mcu200t/src中的system.v顶层文件和rtl/e203中的所有文件夹加入到项目中。

随后,根据目前手头上的开发板的芯片型号选择对应的芯片。引脚约束文件可以暂时先不加入。

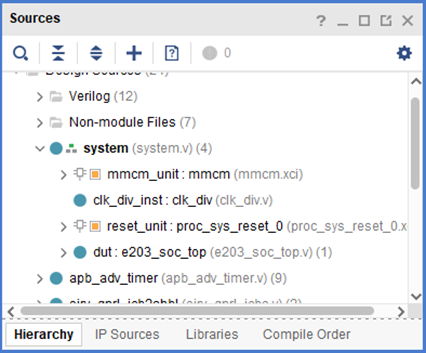

完成创建工程后,将system.v文件设为顶层

例化IP核

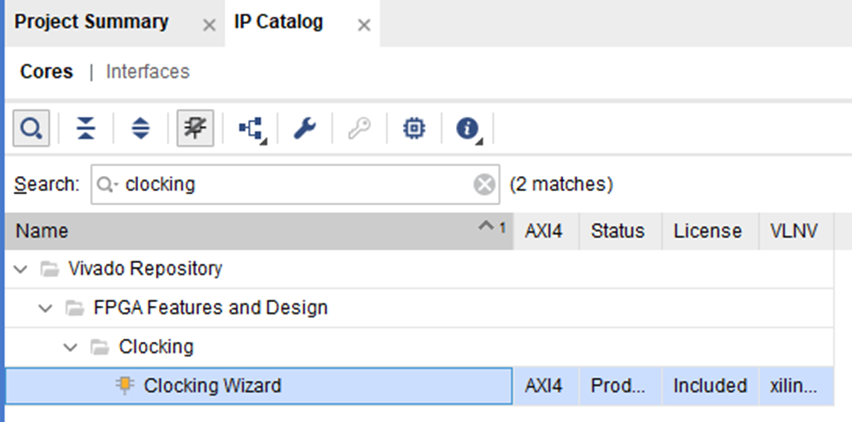

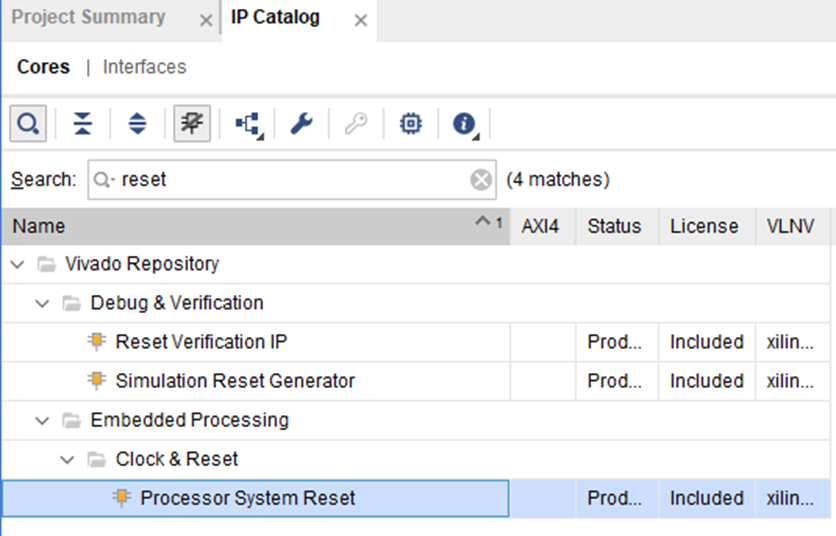

由于蜂鸟内部CLK有两个,分别是16MHz高频时钟和3.2768KHz低频时钟,在FPGA板上只有外部晶振提供时钟,因此需要例化clocking wizard IP核提供时钟,并且例化reset IP。

点击IP Catalog,搜索clocking wizard。

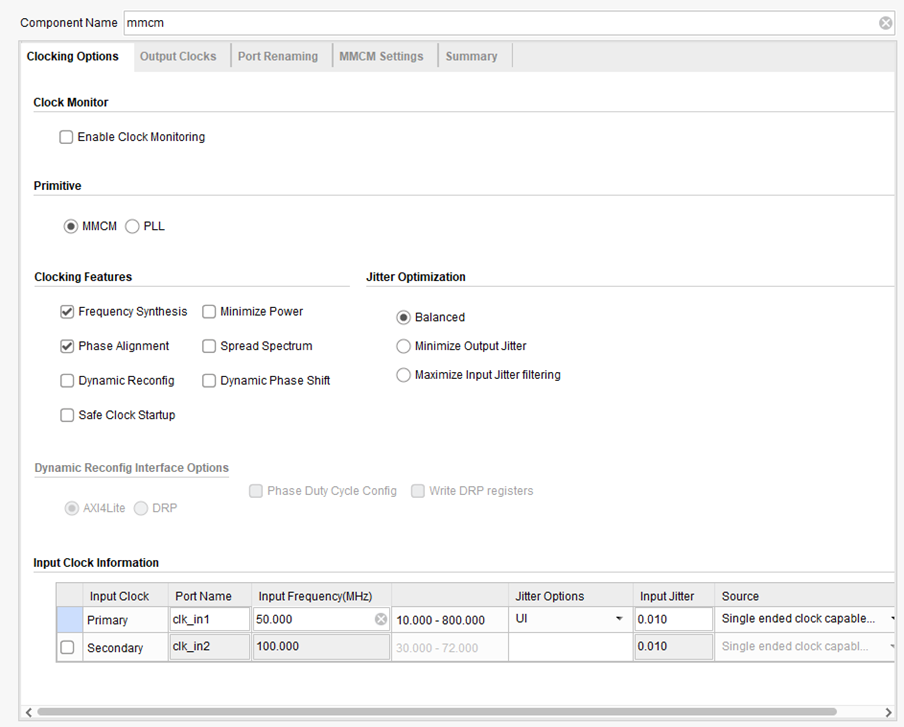

Clocking options设置如下图所示,其中primary input clock输入时钟的频率根据手头上的开发板的主频选择,我们小组暂时使用的是50MHz晶振时钟的FPGA。

Output clocks页面设置如图,其中clock_out1是输出高频时钟16MHz,reset信号要选择activelow,因为system.v中原本设定的reset信号就是activelow的。而低频时钟不能通过mmcm直接生成,需要另外写分频器,后续会讲。

注意,请先将原本system.v的两个原本的例化注释掉,防止重复例化。

使用分频器生成低频时钟

我们小组暂时使用的FPGA开发板主频为50MHz,50M/3.2768K≈1526,如下代码分频可得到3.2768KHz时钟。

module clk_div(

input CLK50MHZ,

input rst_n,

output reg clk_div

);

parameter NUM_DIV = 11'd1526;

reg [10:0] cnt;

always @(posedge CLK50MHZ or negedge rst_n)

if(!rst_n) begin

cnt <= 11'd0;

clk_div <= 1'b0;

end

else if(cnt < NUM_DIV / 2 - 1) begin

cnt <= cnt + 1'b1;

clk_div <= clk_div;

end

else begin

cnt <= 11'd0;

clk_div <= ~clk_div;

end

endmodule

并在system.v中例化该模块

clk_div clk_div_inst(

.CLK50MHZ(CLK50MHZ),

.rst_n(ck_rst),

.clk_div(CLK32768HZ)

);

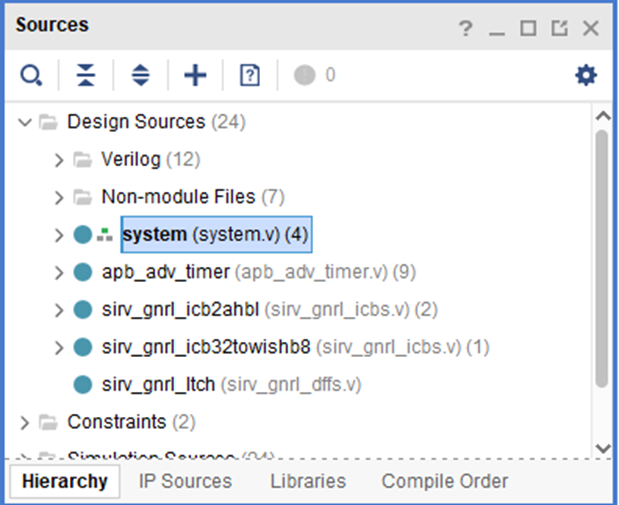

到此,已经做好了IP核例化的相关工作,成功例化后的system.v中的子模块会如下图显示。