报名编号:CICC2469

团队名称:AM

学校名称:广东工业大学

队伍成员:林贤、刘合明、谢泽铭

指导老师:郑欣、高怀恩

环境:Vivado2021.1、NucleiStudio_IDE_202102-win64

内容:ITCM扩容方法及 xxx.elf section .bss' will not fit in region ram解决办法

一, xxx.elf section .bss' will not fit in region ram报错原因

1.这种情况一般是你的软代码太大了,ITCM和DTCM的默认储存为64K,当你的软代码编译完后的可执行文件大 小超过64K,则会爆出这个错误

2.这个问题使用FLASH下载模式是解决不了的,因为IDE手册里很清楚说明了,FLASH下载模式是先将软代码放 到FLASH,然后再搬到ILM执行,最后还是绕不开ILM

二,解决方法(ITCM以及DTCM扩容)

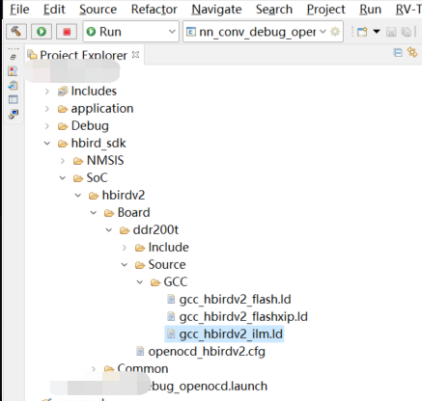

1.首先选定自己使用哪种下载模式,如果是ILM模式的话,在IDE最左侧的工程列表处,选中自己的工程,按下面的路径打开gcc_hbirdv2_ilm.ld这个文件

2.把64K大小扩容,可以写成128K,256K,看自身需求,这里写256K

OUTPUT_ARCH( "riscv" )

ENTRY( _start )

MEMORY

{

ilm (rxai!w) : ORIGIN = 0x80000000, LENGTH = 64K

ram (wxa!ri) : ORIGIN = 0x90000000, LENGTH = 64K

}

OUTPUT_ARCH( "riscv" )

ENTRY( _start )

MEMORY

{

ilm (rxai!w) : ORIGIN = 0x80000000, LENGTH = 256K

ram (wxa!ri) : ORIGIN = 0x90000000, LENGTH = 256K

}

3.改到合适大小后,再进行编译则不会报上述错误

4.软件端改好了后,要在e203内硬件修改实际ITCM和DTCM大小

1.首先打开core下的config.v文件

`define E203_CFG_ITCM_ADDR_WIDTH 18

// // 1024KB have address 20bits wide

// // The depth is 1024*1024*8/64=131072

//`define E203_CFG_ITCM_ADDR_WIDTH 20

// // 2048KB have address 21bits wide

// // The depth is 2*1024*1024*8/64=262144

//`define E203_CFG_ITCM_ADDR_WIDTH 21

`define E203_CFG_DTCM_ADDR_WIDTH 18

//对这两个宏定义修改,本来64K对应16,则128K对应17,256K对应18,这里选择了256K

//不要改得太大,否则FPGA核的储存资源会不够