队伍编号:CICC1753,队伍名称:无所谓对不队

vivado综合后时序为例主要是有两种原因导致:

1,太多的逻辑级

2,太高的扇出

分析时序违例的具体位置以及原因可以使用一些tcl命令方便快速得到路径信息。

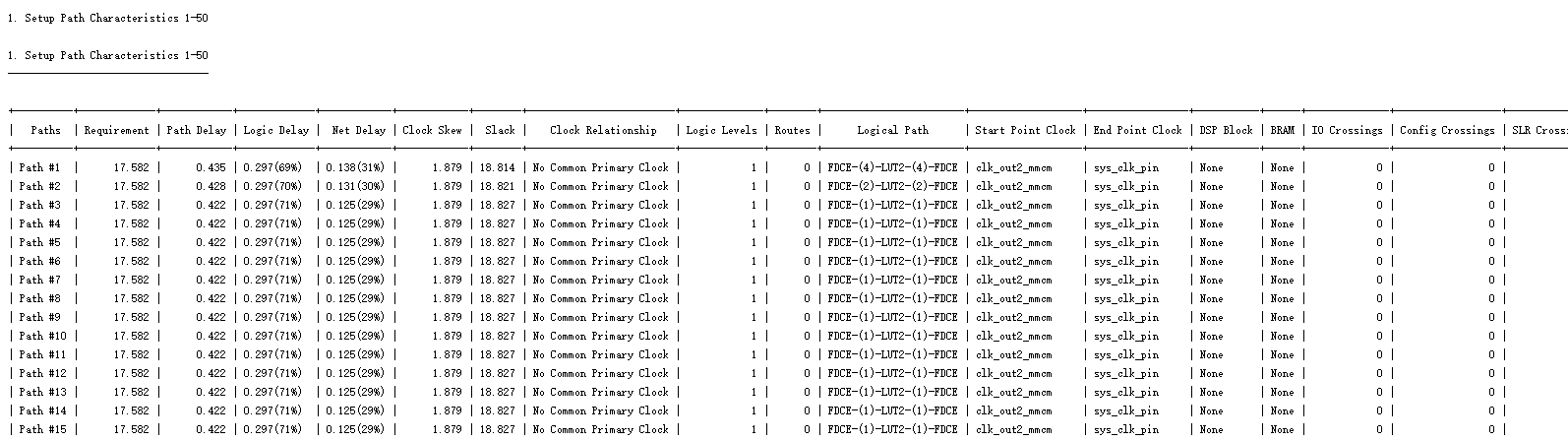

“report_design_analysis -max_paths 50 -setup”此指令可以报告最差的50条setup timing path。

“report_design_analysis -logic_level_distribution -logic_level_dist_paths 5000 -name design_analysis_prePlace”此tcl命令可以对设计中的逻辑级数分布进行分析,进而判断是否存在不满足时序要求的逻辑级数。逻辑级数过多一般可以通过插入寄存器打拍子,分割冗长的组合逻辑。

线延时较长时,一般是因为扇出较大。

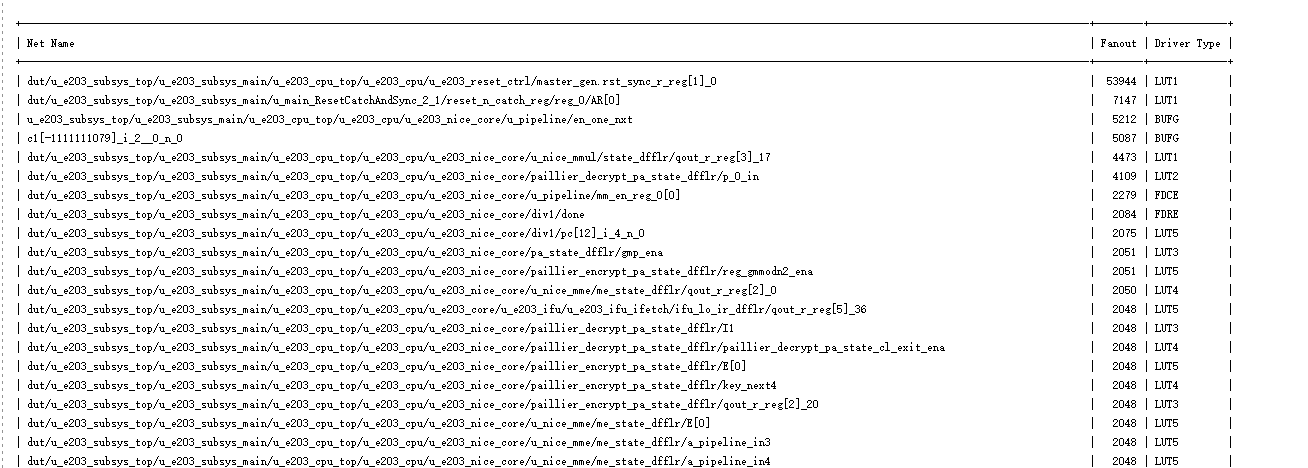

”report_high_fanout_nets -fanout_greater_than 100 -max_nets 100“此tcl命令可以报告扇出大于100的100条最长路径。

命令生成的报告如上,可以分析fanout和驱动类型。对于较大的fanout,最好改为寄存输出。

时序分析有两个主要路径

Intra-clock:同时钟之间的路径分析,需实打实解决。(改善设计,改变综合策略等)

Inter-clock:表示跨时钟路径,在静态分析时,可以将其设计为伪路径,不进行时序分析。