喜欢2次

我们是学堂路三轮车队,报名编号卫CICC1449。这是我们分享的第六篇文章,此前的五篇文章链接如下:

非常感谢此开源论坛,确实收获满满!

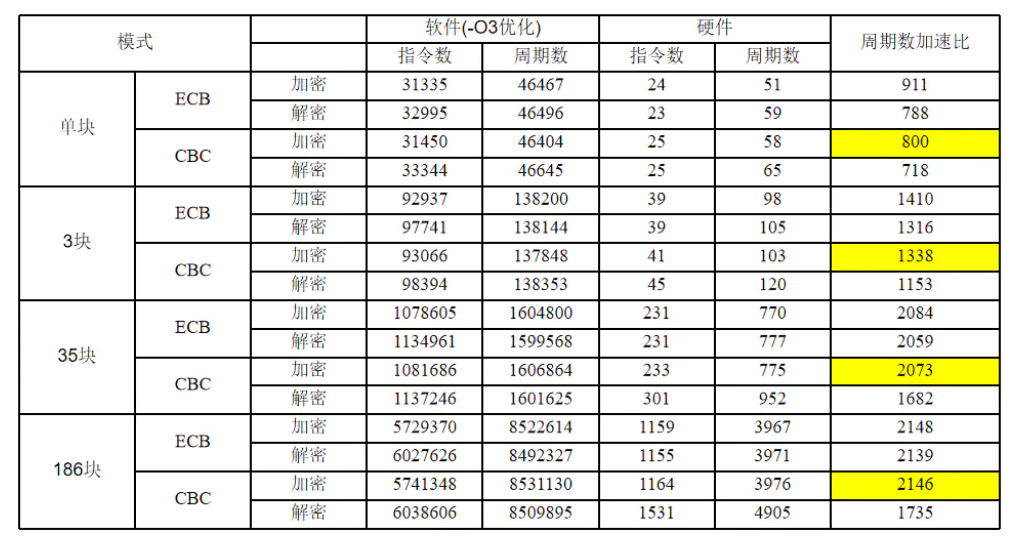

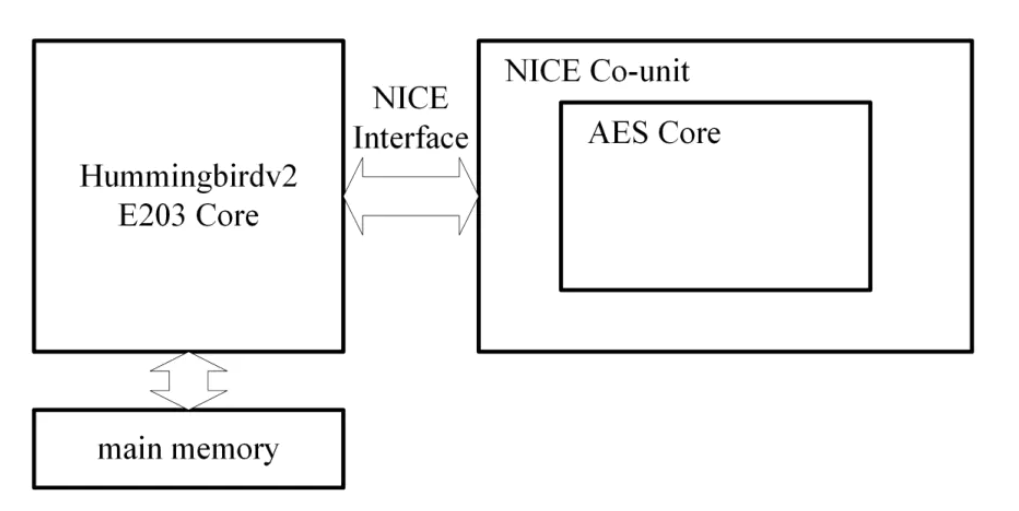

我们设计了基于NICE接口的AES加解密协处理单元,拓展了6条拓展指令,支持EBC、CBC、、CFB、OFB、CTR五种加密模式,和软件相比,速度提高约2000倍。整体框架如下:

工程设计主要分成三个部分:软件上指令拓展、接口调度、硬件协同优化。

我们采用中等粒度方式设计了6条拓展指令,通过适当组合,可以支持五种加解密模式。

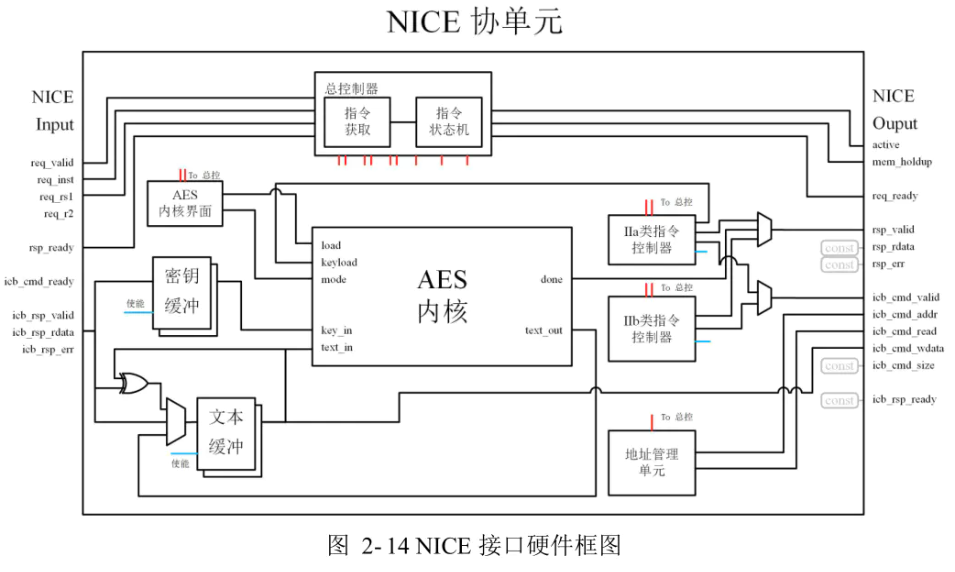

接口实现是工程的难点,需要非常仔细设计其中的数据流和控制流,期间碰到大小端转换问题、文本密钥缓存问题等,总体框图如下:

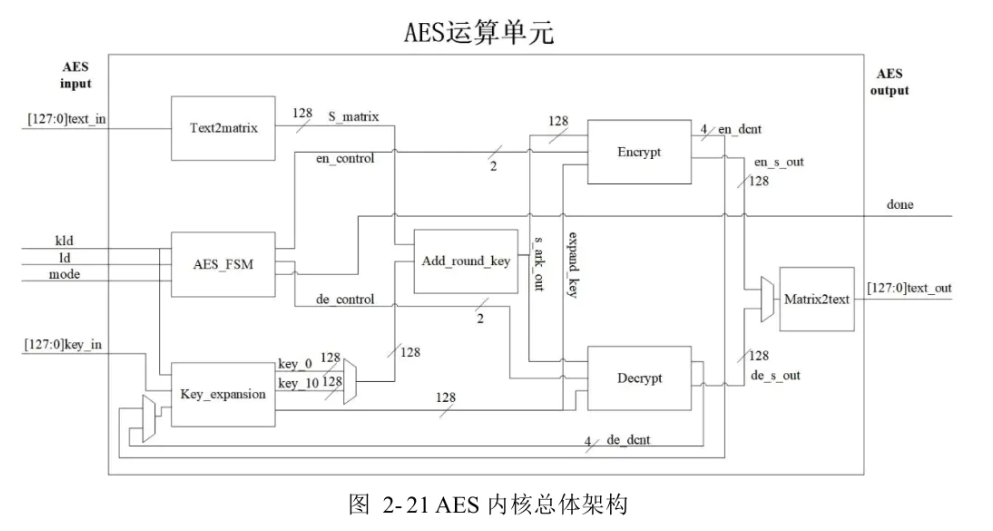

AES的硬件实现有许多开源的项目,但若要取得更高的性能,需要特别设计,比如轮密钥拓展的时序、状态机的控制、密钥缓存的设计等,总体框架如下:

最后测试不同明文块下,ECB、CBC软件和硬件加解密的周期数,取得约2000倍的加速效果。