大家好,我们是华芯极客队,报名编号是CICC3877,本次给大家介绍的是针对AES算法的安全防护设计。

软件中随机延迟的使用通常被认为是对抗侧信道攻击的一般对策,但随机延迟不能阻止攻击,只能让攻击变得复杂。因此基于蜂鸟E203平台的软硬件实现方式,我们的安全防护设计也会从软件和硬件两个方面进行联合设计。

1.

软件层面的防护

软件随机延迟被插入到代码中,以防止攻击能够在没有一些后验分析的情况下确定命令期间特定时刻发生了什么。一般来说包括一个伪循环,其中生成一个随机值,然后递减,直到随机值在执行任何一步的代码之前达到零。下面用汇编语言给出一个代码示例:

这会给整个程序增加很少的额外代码,因为这会将寄存器RND中保存的随机值移动到另一个寄存器(通过累加器),然后递减该值并循环,直到累加器包含零。

2.

硬件层面的防护

随机掩码技术是目前唯一可证安全的技术手段,我们便采用掩码技术作为AES的抗功耗击手段。

掩码技术对加密过程中的中间数据做随机化处理,使攻击者很难采集到有效的功耗曲线,从而无法获取密钥与功耗曲线之间的相关性。为确保加密算法在执行过程中始终安全,全掩码技术是最常用的一种方法。

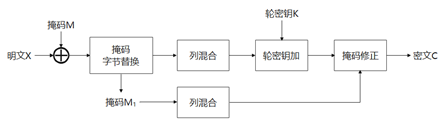

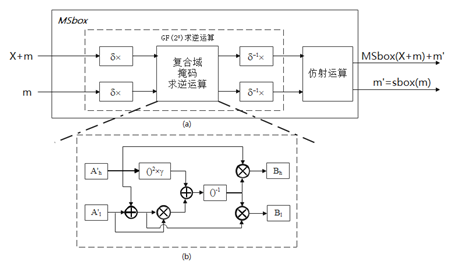

根据AES加解密算法的特点,结合我们提出的运算结构,设计的全掩码AES加解密电路的结构如图1所示。

图1

AES算法中的字节替代模块是整个算法中唯一的非线性变换,不满足f(x+m)=f(x)+f(m),因此需要单独设计。AES的S盒包括仿射运算和GF(2^8)域上的求逆运算,其有限域运算可表示为公式(1)所示形式。

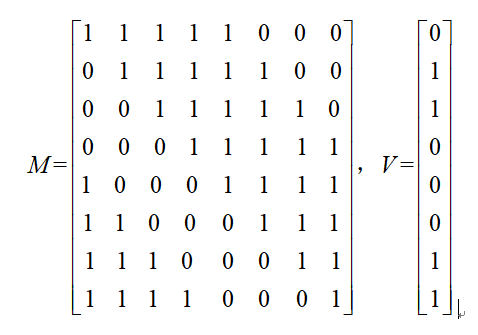

公式(1) Z=M(X)^(-1)+V

式中,X为S盒的输入,Z为AES S盒输出,M和V分别为S盒的仿射矩阵和仿射运算中的常量,可表示为式(2)所示形式。

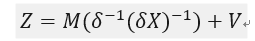

通过分析公式(1)可以看出,S盒实现的关键在于GF(2^8)域上的求逆运算。采用复合域分解技术,将有限域GF(2^8 )上的求逆运算转换到复合域GF((2)^4)^2)上实现,那么式(1)可以变换为式(3)所示形式。

公式(3)

其中,X为S盒输入,δ和δ^(-1)分别为GF(2^8 )到

GF((2)^4)^2) 的映射矩阵和逆映射矩阵。

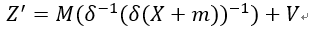

在引入掩码之后,表达式(3)转变为表达式(4)所示形式。

公式(4)

根据表达式(4),AES S盒电路结构图表示为图2所示形式。

图2

实验结果表明,在加入了软硬件防护之后,我们设计的AES掩码算法能够在较小的资源需求的代价下抵抗功耗攻击。

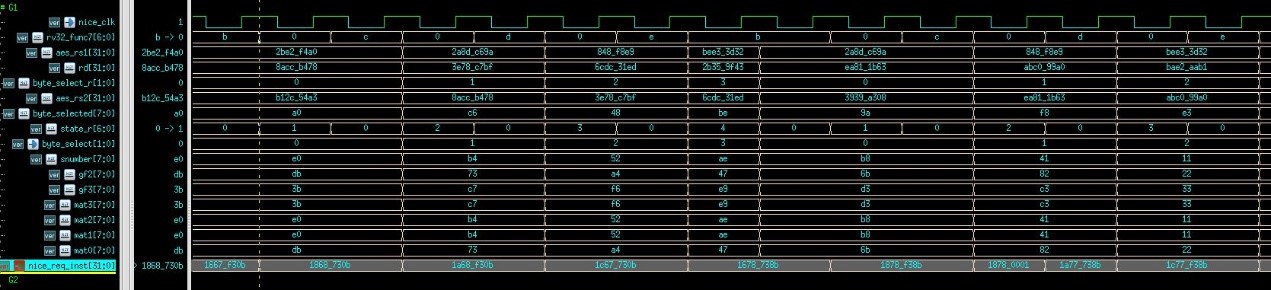

图3 未加掩码防护的AES算法部分波形

图3 未加掩码防护的AES算法部分波形

图4 加掩码防护的AES算法部分波形

图4 加掩码防护的AES算法部分波形