直播过程中,直播间仅限300位名额,由于一下子涌入太多人,这场直播先后经历了没有画面、有画面没有声音、胡老师精心准备的视频播放不出,整个直播时间从一个小时磕磕绊绊延长到了两个半小时。

本次课件《面向物联网的开源RISC-V处理器的设计和开发》

下载地址:

https://eyun.baidu.com/s/3nwvO0rf

密码:3r5d

本次课程胡老师主要从以下几个地方展开讲解

一、关于RISC-V和开源RISC-V内核蜂鸟E203

在2017年的时候,RISC-V在国外已经诞生了很多的开源RISC-V处理器内核,但是在国内一直没有贡献具有影响力的开源内核,这是很令人遗憾的。并且很多国外开源内核也是使用抽象层次比较高的Chisel、BlUESPEC、Systemverilog等语言开发且文档很不完善,不利于本土爱好者和初学者快速上手RISC-V,所以我开发了一个使用工业级Verilog标准开发的开源RISC-V内核(蜂鸟E203)上传至Github,希望能够为国内的科教领域提供一个简单易上手的学习素材。目前蜂鸟E203内核在中国大陆的爱好者、初学者和高校领域已经广泛的被使用和学习起来,为了让越来越多的爱好者可以学习蜂鸟E203 RISC-V处理器内核,为此我们还推出了配套的开发板。

本次直播中涉及到的技术细节很多,本文无法展开进行详述,下文重点对胡老师分享的观点进行分享

二、关于常见的RISC-V的几个误区

误区1:此开发非彼开放

误区2:此Free非彼Free

误区3:此OpenSource非彼OpenSource

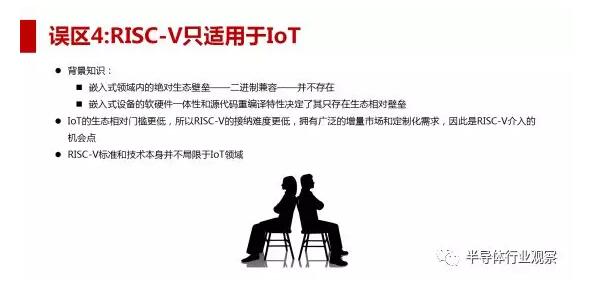

现在很多说法称,RISC-V只适合IoT,或者说特别适合,这二种说法其实都不准确。首先要提出一个“绝对壁垒”和“相对壁垒”的概念,如果在某个领域有严格的二进制兼容要求,多老的程序在新系统上都要求可以跑,那这是一个有绝对壁垒的生态。但是在嵌入式领域内,这种绝对生态壁垒(二进制兼容)并不存在,嵌入式设备的软硬件一体性和源代码重编译特性决定了其只存在生态的相对壁垒。

误区5:RISC-V等于新的设计语言和方法学

过分强调新的设计语言和方法,让很多人误解成RISC-V必须要用新的设计语言和方法进行设计,从而引发一些不必要的争议,偏离了讨论的方向。正如前边反复强调的,RISC-V只是一份开放指令集标准,与新的设计语言和方法学毫无关系。所以建议本土产业更需专注解决核心产业有和无的问题,将RISC-V与新的设计语言和设计方法打包宣传会带来很多噪音,对于RISC-V的推广并无裨益。

这也是RISC-V很常见的误区和标签,到目前为止,人类已知的商业模式无非是卖产品、卖服务或流量变现。芯片行业主要是前两种,芯片行业通行的IP模式依赖的版税方式,本质上等于卖服务。

所以说,对于商业IP而言,没有IP版税,如何能保证产品品质以及对客户的长期负责,甚至还可能让用户认为,便宜没好货。

三、关于RISC-V的未来趋势

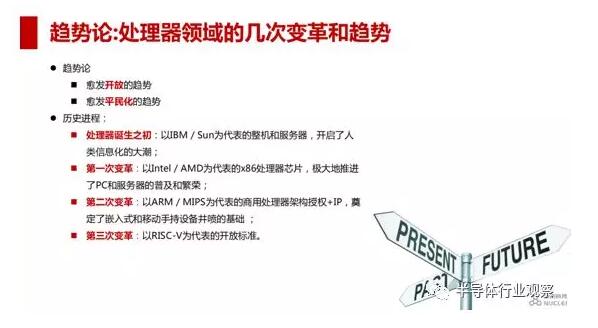

让我们回顾历史:

从开放趋势角度来看,RISC-V的目标是成为一种由基金会维护的开放通用的指令集架构,按照产业变革路径,整机到处理器芯片到处理器IP,最终到RISC-V标准,是历史的必然。所以,从它诞生开始,因其开放,得到了诸多大型公司和社区的支持,因此生态发展迅速,当生态建设不再由一家公司而是由全行业推动时,其速度远远高于以往由单一商业公司推动,且成本被均摊。

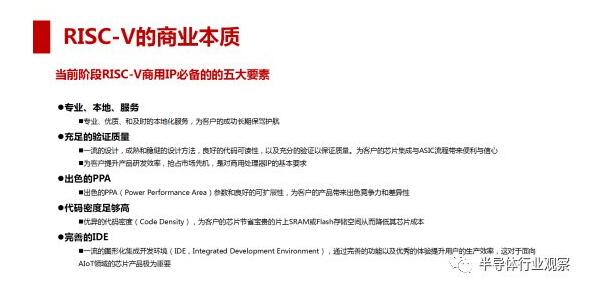

四、关于RISC-V的商业本质