在学习“Nuclei™ N100 系列处理器内核快速集成手册”时,在第6章进行实验出错warning

------------------------------------------------------------------------------------------------------------------------------------------

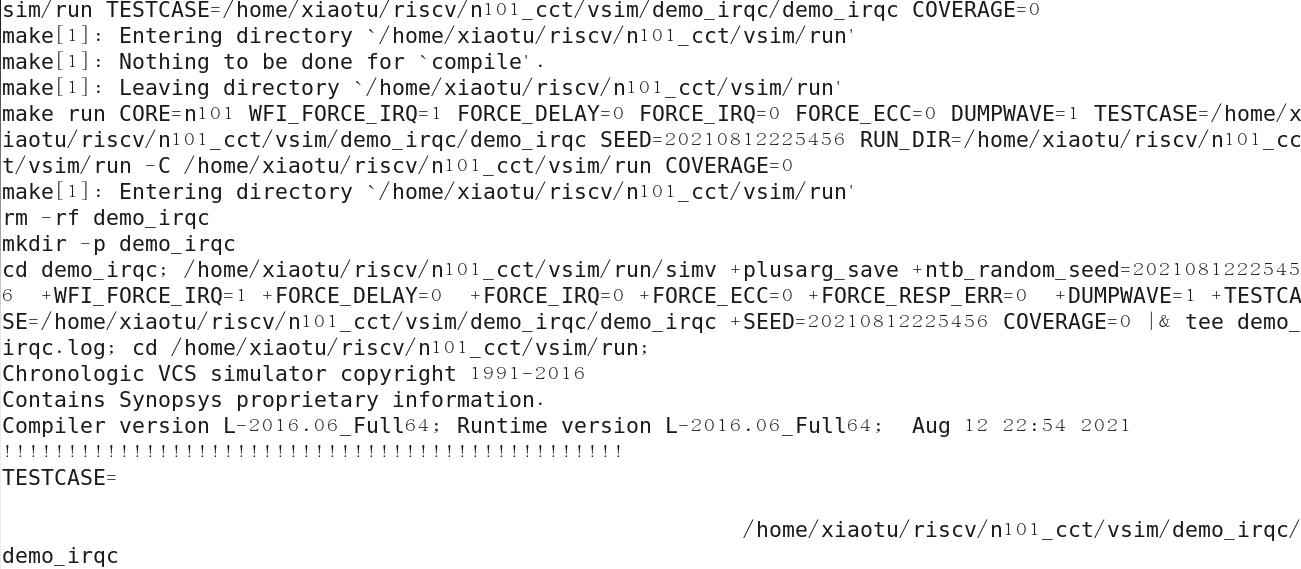

Warning-[STASKW_RMIEAFL] Illegal entry

/home/xiaotu/riscv/n101_cct/vsim/run/../install/tb/tb_mem_init.v, 28

Illegal entry found at file

/home/xiaotu/riscv/n101_cct/vsim/demo_irqc/demo_irqc.verilog line 1 while

executing $readmem.

Please ensure that the file has proper entries.

ILM 0x00: xxxxxxxx

ILM 0x01: xxxxxxxx

ILM 0x02: xxxxxxxx

ILM 0x03: xxxxxxxx

ILM 0x04: xxxxxxxx

ILM 0x05: xxxxxxxx

ILM 0x06: xxxxxxxx

ILM 0x07: xxxxxxxx

ILM 0x16: xxxxxxxx

ILM 0x20: xxxxxxxx

SEED = 20210812225456

FORCE_DELAY= 0

*Verdi3* Loading libsscore_vcs201606.so

*Verdi3* : FSDB_GATE is set.

*Verdi3* : FSDB_RTL is set.

*Verdi3* : Enable Parallel Dumping.

FSDB Dumper for VCS, Release Verdi3_L-2016.06-1, Linux x86_64/64bit, 07/10/2016

(C) 1996 - 2016 by Synopsys, Inc.

*Verdi3* : Create FSDB file 'tb_top.fsdb'

*Verdi3* : Begin traversing the scope (tb_top), layer (0).

*Verdi3* : Enable +mda dumping.

*Verdi3* : End of traversing.

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

TESTCASE= /home/xiaotu/riscv/n101_cct/vsim/demo_irqc/demo_irqc

FORCE_IRQ= 0

FORCE_RESP_ERR= 0

WFI_FORCE_IRQ= 1

Warning-[STASKW_RMIEAFL] Illegal entry

/home/xiaotu/riscv/n101_cct/vsim/run/../install/tb/tb_mem_init.v, 70

Illegal entry found at file

/home/xiaotu/riscv/n101_cct/vsim/demo_irqc/demo_irqc.verilog line 1 while

executing $readmem.

Please ensure that the file has proper entries.

Warning-[STASKW_RMIEAFL] Illegal entry

/home/xiaotu/riscv/n101_cct/vsim/run/../install/tb/tb_mem_init.v, 70

Illegal entry found at file

/home/xiaotu/riscv/n101_cct/vsim/demo_irqc/demo_irqc.verilog line 1 while

executing $readmem.

Please ensure that the file has proper entries.

Time Out !!!

$finish called from file "/home/xiaotu/riscv/n101_cct/vsim/run/../install/tb/tb_top.v", line 145.

$finish at simulation time 20000000000

V C S S i m u l a t i o n R e p o r t

Time: 200000000000 ps

CPU Time: 12.950 seconds; Data structure size: 2.8Mb

Thu Aug 12 22:55:12 2021

make[1]: Leaving directory `/home/xiaotu/riscv/n101_cct/vsim/run'

--------------------------------------------------------------------------------------------------------------------------------------------------

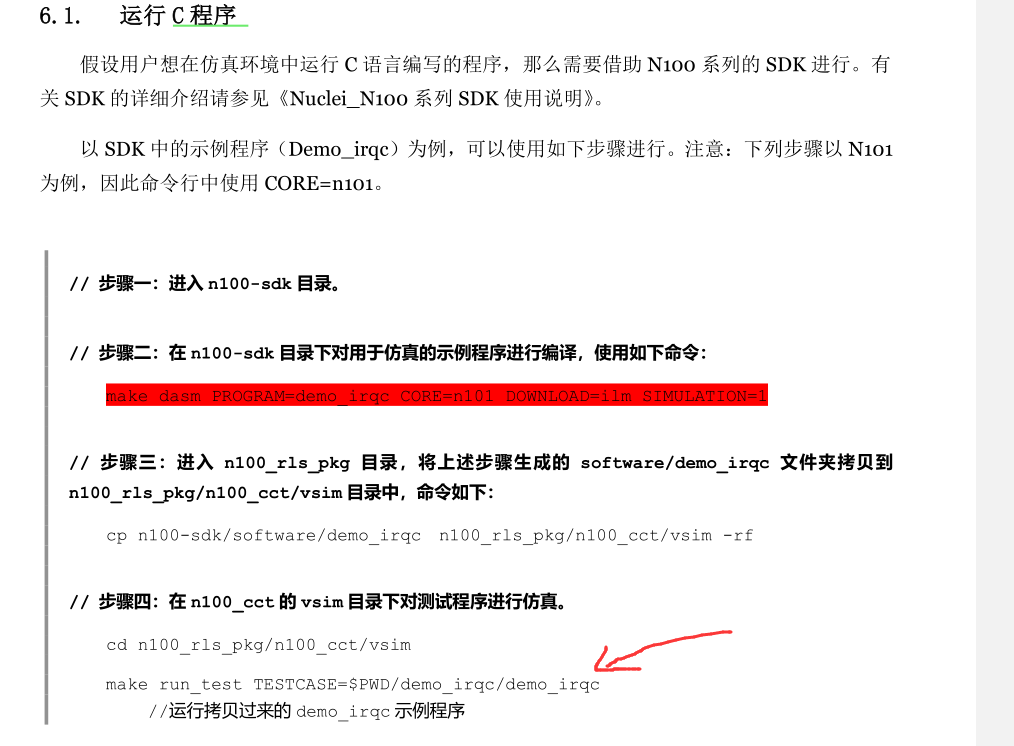

步骤一二三均可正确执行,但到第四步make run_test TESTCASE=$PWD/demo_irqc/demo_irqc,就出warning。

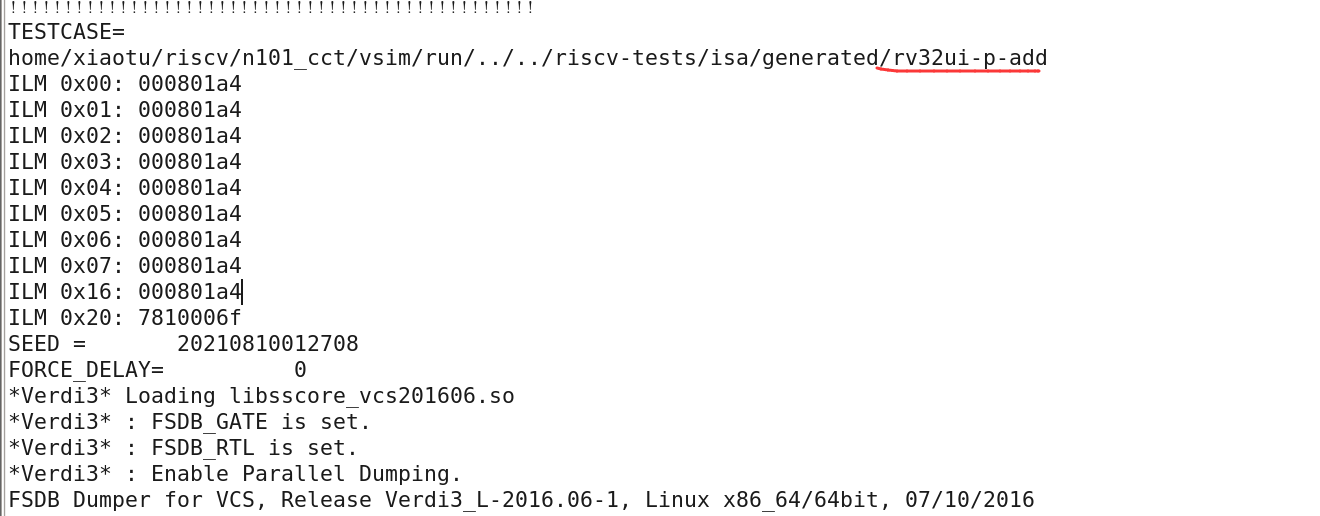

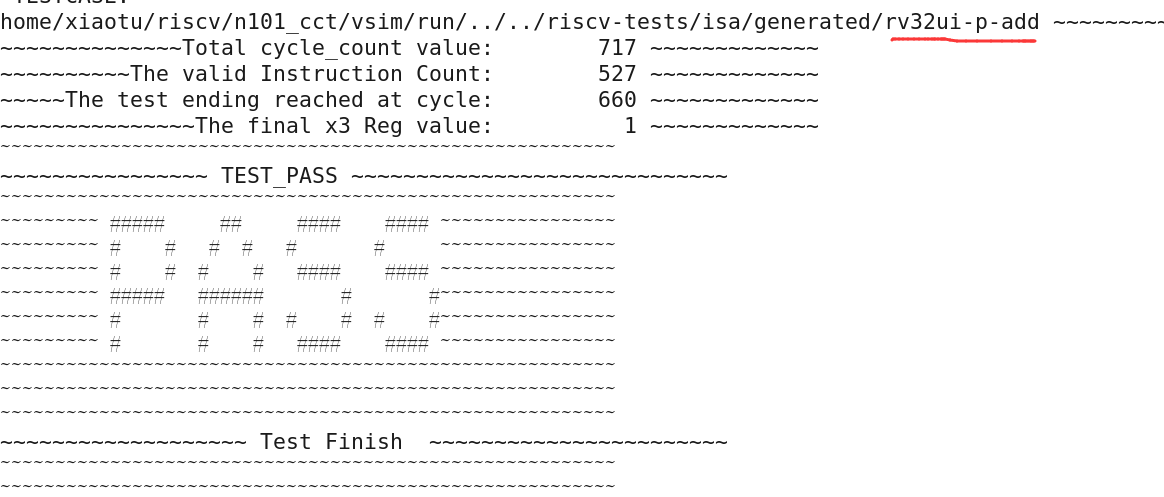

运行case=rv32ui-p-add就没有问题显示PASS,“demo_irqc.verilog”与“rv32ui-p-add.verilog”文件里面的16进制格式写法一样,但是一个行,一个不行。

是在不清楚问题出在哪里?!